# City Research Online

## City, University of London Institutional Repository

**Citation:** Kassanos, P., Constantinou, L., Triantis, I. & Demosthenous, A. (2014). An Integrated Analog Readout for Multi-Frequency Bioimpedance Measurements. IEEE Sensors Journal, 14(8), pp. 2792-2800. doi: 10.1109/jsen.2014.2315963

This is the accepted version of the paper.

This version of the publication may differ from the final published version.

Permanent repository link: https://openaccess.city.ac.uk/id/eprint/14837/

Link to published version: https://doi.org/10.1109/jsen.2014.2315963

**Copyright:** City Research Online aims to make research outputs of City, University of London available to a wider audience. Copyright and Moral Rights remain with the author(s) and/or copyright holders. URLs from City Research Online may be freely distributed and linked to.

**Reuse:** Copies of full items can be used for personal research or study, educational, or not-for-profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

City Research Online: <a href="http://openaccess.city.ac.uk/">http://openaccess.city.ac.uk/</a> <a href="publications@city.ac.uk/">publications@city.ac.uk/</a>

An Integrated Analog Readout for Multi-Frequency

# Bioimpedance Measurements

Panagiotis Kassanos, *Member, IEEE*, Loucas Constantinou, *Student Member, IEEE*, Iasonas F. Triantis, *Member, IEEE*, and Andreas Demosthenous, *Senior Member, IEEE*

Abstract—Bioimpedance spectroscopy is used in a wide range of biomedical applications. This paper presents an integrated analog readout, which employs synchronous detection to perform galvanostatic multi-channel, multi-frequency bioim-pedance measurements. The circuit was fabricated in a 0.35-\$\mu\eta\$ CMOS technology, occupying an area of 1.52 mm². The effect of random dc offsets is investigated, along with the use of chopping to minimize them. Impedance measurements of a known RC load and skin (using commercially available electrodes) demonstrate the operation of the system over a frequency range up to 1 MHz. The circuit operates from a  $\pm 2.5$  V power supply and has a power consumption of 3.4-mW per channel.

Index Terms—Analog circuit design, bioimpedance, impedance spectroscopy, multi-frequency, readout, synchronous detection.

#### I. INTRODUCTION

**B**IOIMPEDANCE measurement is an established technique with a wide range of medical applications. These include cancerous tissue characterization and detection [1], electrical impedance tomography (EIT) [2], total body analysis systems [3], gas sensors [4], impedimetric biosensors [5] and various lab-on-a-chip applications [6]. In human tissue measurements [1]-[3] typically a galvanostatic approach (inject current, measure voltage) is used in order to limit the current injected to the tissue and thus, adhere to medical safety regulations with the maximum allowable current being a function of frequency [7]. The current driver input signal can either be a single frequency sinusoid or a multi-frequency signal [8].

Impedance can be described by its magnitude and phase or, alternatively, by its real and imaginary parts. Magnitude/phase measurement is the simplest and most straightforward tech-nique. The magnitude can be calculated using a peak

Manuscript received January 27, 2014; revised March 27, 2014; accepted April 3, 2014. This work was supported in part by the U.K. Engineering and Physical Sciences Research Council under Grant EP/G061629/1 and in part by a Ph.D. + Fellowship. The associate editor coordinating the review of this paper and approving it for publication was Prof. Octavian Postolache.

- P. Kassanos was with the Department of Electronic and Electrical Engineer-ing, University College London, London WC1E 7JE, U.K. He is now with The Hamlyn Centre, Institute of Global Health Innovation, Imperial College, London SW7 2AZ, U.K. (e-mail: <a href="mailto:p.kassanos@imperial.ac.uk">p.kassanos@imperial.ac.uk</a>).

- L. Constantinou and A. Demosthenous are with the Department of Electronic and Electrical Engineering, University College London, London WC1E 7JE, U.K. (e-mail: loucas.constantinou.10@ucl.ac.uk; a.demosthenous@ucl.ac.uk).

- I. F. Triantis is with the Department of Electrical and Electronic Engineering, City University, London EC1V 0HB, U.K. (e-mail: <a href="mailto:iasonas.triantis.1@city.ac.uk">iasonas.triantis.1@city.ac.uk</a>).

detector [9] or by full-wave rectification and subsequent low-pass filtering [10] of the measured sinusoidal voltage across the load. Calculation of the phase requires a reference signal in-phase  $(0^{\circ})$  to the one applied to the impedance under test. Comparison of square wave versions of this reference signal with the measured one across the impedance at each frequency with a phase detector provides a measure of the impedance phase. The phase output can then be processed

further as discussed in [10]. Hence, a magnitude/phase measurement requires two different measurement channels, each with poten-tially different sources of error, requiring different techniques to address them. Synchronization is only important for the phase channel. Multi-frequency measurements require the use of bandpass filters in this topology, with a dedicated channel for each frequency.

Real/imaginary part measurement is more complicated. A methodology to obtain the real and imaginary components is the sampling technique [11], [12]. Since the excitation signal frequency, phase and amplitude are typically known, there is no need to perform a fast Fourier transform (FFT). By sampling at the exact instances where the input frequency components reach their peak value and cross zero, the real and imaginary components are obtained. This technique is known as synchronous sampling (SS). Obtaining these samples in both half cycles of the period eliminates offsets by averaging the measurements [12]. Averaging the measurements within the full period of a multi-frequency signal allows the calcula-tion of the real and imaginary components at each frequency using a single channel [12], which is an advantage over other techniques. However, accurate synchronization for obtaining the samples is essential, which can be challenging, particularly at high frequencies [11].

Synchronous detection (SD, also known as lock-in, phase sensitive and quadrature demodulation) is a popular technique for this type of measurement and is well established [4], [13]-[15]. Multiplication of the measured sinusoidal voltage signal by an in-phase (0°) and a quadrature (90°) signal is required to calculate the real and imaginary component values, respectively, at the frequency of the applied signal (in a single frequency measurement) or with a frequency of interest which is present in the applied signal (in a multi-frequency measurement). In this way the readout locks to a specific frequency component, demodulating it to dc with all other frequency components being modulated to higher frequencies (including electrode dc voltages). The multiplier output needs to be lowpass filtered in order to reject all frequency components generated by the multiplication and

1

any other frequencies present, and keep the dc component proportional to the real or imaginary part of the impedance. The combination of the multiplication and the lowpass filter effectively imposes a frequency selective property to the system. Hence, no additional bandpass filters are required as in the magnitude/phase system. Once again, two channels are required, which need to be accurately matched. In this case, however, the channels are identical and thus, sources of error are common. In applications where the impedance does not change rapidly, a single channel can be used, by switching the demodulation signal between 0° and 90°. The cutoff frequency and order of the filter for the abovementioned systems can be selected by considering the lowest frequency of interest and the settling-time required, defined by the biological system being investigated [8].

One of the challenges in such a system is the design of the current driver [16], [17]. The amplitude of the drive current should remain constant irrespective of the impedance mag-nitude of the load and the frequency (in order to eliminate the need to constantly measure it). Another performance characteristic of the current driver is the phase difference between the output current signals relative to the input applied signals. Depending on the impedance measurement (readout) topology, the current driver phase error may need to be kept to a minimum, as it can introduce errors in the calculation of the measured impedance.

EIT for neonatal lung function monitoring, which is one of the target applications, requires a large number of measure-ments from 32 or more electrodes. To avoid issues associated with physiological drift, the measurements should be per-formed rapidly. This dictates a system capable of simultaneous measurements of the real and imaginary components of the load impedance (typically <100  $\Omega$  to > 5 k O) at multiple frequencies, with a frequency range up to 1 MHz [18]. A minimum of two frequencies are required to perform frequency differencing measurements for imaging [19]. The minimization of parasitics (e.g. due to cabling), and the need for a multi-channel readout (for multi-frequency opera-tion), portability and miniaturization, necessitate the develop-ment of custom designed integrated circuits for bioimpedance applications, which can also offer the option to embed the instrumentation on the electrodes. This paper presents an integrated multi-channel analog readout employing SD for multi-frequency bioimpedance measurements, which to the authors' knowledge is the first of its kind. The performance of the fabricated chip (in a 0.35-<sup>^</sup>m CMOS technology) is demonstrated with both single- and multi-frequency signals. Chopping is used to minimize the dc offset voltages of the on-chip instrumentation amplifiers (IAs). The effect of the offsets on the measurement is assessed.

The paper is a development of [14] and presents details of the circuit and measurements from a second version of the chip design. The rest of the paper is organized as follows. Section II presents the system architecture and the theory of operation. Section III presents simulated and measured results showing the electrical performance of the fabricated samples for single-and dual-frequency excitation. The chip was combined with a current driver to form a tetrapolar impedance measurement system. Measurements show impedance responses of an RC circuit and skin impedance (obtained with commercial skin electrodes). The discussion and the conclusion in Sections IV and V, respectively, complete the paper.

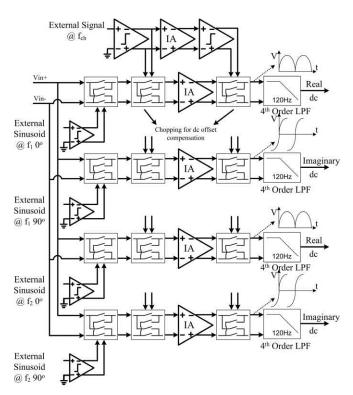

Fig. 1. System block diagram of the multi-frequency analog readout. The voltage versus time curves are examples of the outputs of the amplifiers when the offset is zero, the chopping is disabled and input signal has no phase shift.

Fig. 1 shows the block diagram of the analog readout. In a single frequency scenario the SD modulator output for the real (VsD\_Re) and the imaginary (VsDJm) channels are [15]

$$V_{\text{SD\_Re}} = \frac{A}{2} \left[ \cos \left( \phi_1 \right) - \cos \left( 2\omega_1 t - \phi_1 \right) \right] + C \sin \left( \omega_1 t \right)$$

$$V_{\text{SD\_Im}} = \frac{A}{2} \left[ \cos \left( \phi_1 + \frac{\pi}{2} \right) - \cos \left( 2\omega_1 t - \phi_1 + \frac{\pi}{2} \right) \right]$$

$$+ C \sin \left( \omega_1 t + \frac{\pi}{2} \right), \tag{1}$$

where A is the amplitude of the voltage across the electrodes, ^1 is the phase delay due to the impedance at angular frequency  $\omega_I$  and C is the dc voltage of the electrode. For brevity, only the real part is considered in the following equations. In a dual-frequency scenario where there are two frequency components present [ $f_I = (\omega_I/2\pi)$  with amplitude A and  $f_2 = (\omega_2/2\pi)$  with amplitude B] and the signal is demodu-lated with a frequency  $f_I$ , then the real part becomes

$$V_{\text{SD-Re}} = \frac{A}{2} \left[ \cos (\phi_1) - \cos (2\omega_1 t - \phi_1) \right] + \frac{B}{2} \left[ \cos ((\omega_1 - \omega_2) t + \phi_2) - \cos ((\omega_1 + \omega_2) t - \phi_2) \right] + C \sin (\omega_1 t).$$

(2)

The signal component of interest is the dc value equal to  $\frac{A}{2}\cos(\phi_1)$  for the real part (and  $\frac{A}{2}\cos(\phi_1+\frac{\pi}{2})$  for the imaginary part).

Amplification and lowpass filtering can be combined as in [20]. However, a high common-mode rejection ratio (CMRR) is required in order to reject inevitable common-mode signals generated at the recording electrodes. To satisfy this, a current-feedback IA is used as in [10], [13], and [14] with digitally programmable gains of 10, 75, 140 and 200 V/V. The IA circuit topology used in this design is presented and characterized in [21]. In order to eliminate the effect of the IA phase delay, demodulation is performed before amplification. A multistage clockless comparator [10] provides a square-wave drive to the mixer switch (modulator). The comparator is driven by a sinusoidal signal.

The dc offset of the IA should be minimized to obtain an accurate measurement. The dc offset is random and varies channel-to-channel and from chip-to-chip. Furthermore, temperature variations, aging and power supply instability could cause the dc offset to fluctuate. To minimize the effect of the dc offset, chopping is employed [22]. The signal of interest is modulated by a carrier signal and this is subsequently amplified by the IA. The signal at the output of the IA contains the amplified signal plus any dc offset of the IA. This is then modulated again with the same carrier (same frequency and phase). In this way, the dc offset is modulated to the frequency of the carrier, while the signal of interest is demodulated back to its original frequency. In practice, the limited bandwidth of the amplifier contributes to high frequency glitches. Thus, the phase delay of the amplifier should be considered. To limit the glitches, the chopping frequency should be within the zero phase delay band of the amplifier. Alternatively, the chopping signal needs to be phase shifted by a phase equal to the ampli-fier phase at that frequency through a delay line or a phase shifter [22]. In the present implementation a path consisting of two comparators and an identical IA in between them is used to drive the choppers and thus, reduce the effect of the amplifier phase delay to the chopping. This structure is shown at the top of Fig. 1. A square wave signal from an external signal generator is used for chopping. All other frequencies resulting from the modulation and demodulation processes are suppressed by the following lowpass filter. The filter uses a chain of two biquadratic filters as in [10]. When (1) is multiplied by a sinusoidal signal of frequency  $f_{ch} = \omega_t \pm i/2\pi$  and unity amplitude the output of the first chopper is

$$V_{\text{Ch1\_Re}} = \frac{A}{2} \cos(\phi_1) \sin(\omega_{\text{ch}} t) - \frac{A}{4} \left[ \sin((2\omega_1 + \omega_{\text{ch}}) t - \phi_1) - \sin((2\omega_1 - \omega_{\text{ch}}) t - \phi_1) \right] + \frac{C}{2} \left[ \cos((\omega_1 - \omega_{\text{ch}}) t) - \cos((\omega_1 + \omega_{\text{ch}}) t) \right].$$

(3)

If two frequencies are present, using (2), the output of the first chopper is

$$V_{\text{Ch1},\text{Re}} = \frac{A}{2}\cos(\phi_1)\sin(\omega_{\text{ch}}t)$$

$$-\frac{A}{4} \left[ \sin \left( (2\omega_{1} + \omega_{\text{ch}}) t - \phi_{1} \right) - \sin \left( (2\omega_{1} - \omega_{\text{ch}}) t - \phi_{1} \right) \right] + \frac{B}{4} \left[ \sin \left( (\omega_{2} - \omega_{1} + \omega_{\text{ch}}) t - \phi_{2} \right) - \sin \left( (\omega_{2} - \omega_{1} - \omega_{\text{ch}}) t - \phi_{2} \right) - \sin \left( (\omega_{2} + \omega_{1} + \omega_{\text{ch}}) t - \phi_{2} \right) + \sin \left( (\omega_{2} + \omega_{1} - \omega_{\text{ch}}) t - \phi_{2} \right) \right] + \frac{C}{2} \left[ \cos \left( (\omega_{1} - \omega_{\text{ch}}) t \right) - \cos \left( (\omega_{1} + \omega_{\text{ch}}) t \right) \right].$$

(4)

The  $V_{\text{ChL-Re}}$  signals in (3) and (4) are then amplified with a gain G and the dc offset voltage of the IA. D, is added to the signal. Subsequently, the signal is multiplied again by the same chopping signal. The signal before the lowpass filter is

$$V_{\text{Ch2\_Re}} = \frac{G \cdot A}{4} \left[ \cos (\phi_1) - \cos (2\omega_{\text{ch}}t - \phi_1) \right] + \frac{G \cdot A}{8} \left[ \cos ((2\omega_1 - 2\omega_{\text{ch}}) t - \phi_1) \right] + \cos ((2\omega_1 + 2\omega_{\text{ch}}) t - \phi_1) - \cos (2\omega_{\text{ch}}t - \phi_1) - \cos(2\omega_{\text{ch}}t + \phi_1) \right] + \frac{G \cdot C}{4} \left[ 2\sin (\omega_1 t) - \sin ((\omega_1 - 2\omega_{\text{ch}}) t) \right] - \sin ((\omega_1 + 2\omega_{\text{ch}}) t) \right] + D \sin (\omega_{\text{ch}}t).$$

(5)

If two frequencies are present, using (4), the output of the second chopper is

$$\frac{G \cdot A}{4} \left[ \cos (\phi_{1}) - \cos (2\omega_{\text{ch}}t - \phi_{1}) \right]

+ \frac{G \cdot A}{8} \left[ \cos ((2\omega_{1} - 2\omega_{\text{ch}})t - \phi_{1}) \right]

+ \cos ((2\omega_{1} + 2\omega_{\text{ch}})t - \phi_{1})

- \cos (2\omega_{\text{ch}}t - \phi_{1}) - \cos (2\omega_{\text{ch}}t + \phi_{1}) \right]

+ \frac{G \cdot B}{8} \left[ 2\cos ((\omega_{2} - \omega_{1})t - \phi_{2}) \right]

- \cos ((\omega_{2} - \omega_{1} + 2\omega_{\text{ch}})t - \phi_{2})

- \cos ((\omega_{2} - \omega_{1} - 2\omega_{\text{ch}})t - \phi_{2}) \right]

- 2\cos ((\omega_{2} + \omega_{1})t - \phi_{2})

+ \cos ((\omega_{2} + \omega_{1} + 2\omega_{\text{ch}})t - \phi_{2}) \right]

+ \cos ((\omega_{2} + \omega_{1} - 2\omega_{\text{ch}})t - \phi_{2}) \right]

+ \frac{G \cdot C}{4} \left[ 2\sin (\omega_{1}t) \right]

- \sin ((\omega_{1} - 2\omega_{\text{ch}})t) - \sin ((\omega_{1} + 2\omega_{\text{ch}})t) \right]

+ D\sin (\omega_{\text{ch}}t).$$

(6)

In (1) to (6), the chopping and SD multiplication signals are considered as pure sinusoids for simplicity. In reality these are square wave signals, which contain many harmonic com-ponents. More detailed expressions for these multiplications are presented in [13]. At the filter output, there will be a small ripple with the same frequency as the carrier signal. Its amplitude depends on the offset value, the cutoff frequency of the lowpass filter and the frequency of the carrier signal used to perform the chopping function [23]. The lowpass filtered output dc signal (Vdcout) of the chopped lock-in amplifier

needs to be divided by G and a  $2/\pi$  factor resulting from the series of modulation and demodulation stages, to obtain the actual dc component ( $V_0$ ). This is equal to

$$V_{\rm o} = \frac{\pi}{2G} V_{\rm dc\_out}. \tag{7}$$

Charge injection mismatch due to mismatch between the chop-ping clock lines, and thus the parasitic capacitances associated with these, leads to residual offset. This can be reduced by minimizing the parasitic capacitances and with a symmetric layout of the chopping clock wires [23]. This source of residual offset is also a function of the chopping frequency and the on-resistance (R<sub>on</sub>) of the input chopper switches, being directly proportional to both. Another source of charge injec-tion is parasitic channel charge redistribution and capacitive feedthrough in the switches in the choppers [22], [23]. The former is directly proportional to the width and length product of the transistors and the latter is directly proportional to their gate-to-source capacitance (and thus also the area of the tran-sistor). Although these errors could be reduced by using min-imum size transistors, this solution leads to a high Ron.Other techniques to minimize charge injection errors include the use of dummy switches, transmission gates (leading to a lower  $R_{\text{on}}$ ), differential topologies, the use of a delayed demod-ulation signal or a guard band in the demodulation signal and spike filtering [22], [23]. In this implementation a fully-differential architecture and transmission gate switches are used. To improve matching, common-centroid layout is used. In total there are four channels, two for measuring the real and imaginary parts at frequency  $f_1$  and the other two at  $f_2$ .

#### III. RESULTS

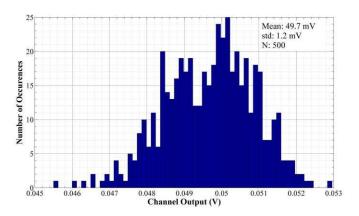

To examine the performance of the circuit under process variations and device mismatch, a single channel (see Fig. 1) was simulated with an input sinusoidal signal of 1 kHz frequency and 50 mV amplitude. The signal was demodu-lated with an in-phase square wave (0°) of 1 kHz frequency generated by the comparator. The mixer switches performing the chopping were driven by a square wave of 10 kHz frequency, as shown in Fig. 1. The nominal output (i.e., with no mismatch) of the channel, using (7), should have a dc value of approximately 50 mV. The result of the Monte Carlo simulation for 500 runs with both process variations and mismatch is shown in the histogram in Fig. 2. The channel output has a mean value of 49.7 mV and a standard deviation (std) of 1.2 mV. 97 % of the runs are within a 5% deviation from the mean value. This result demonstrates the robustness of the design under process variations and device mismatch.

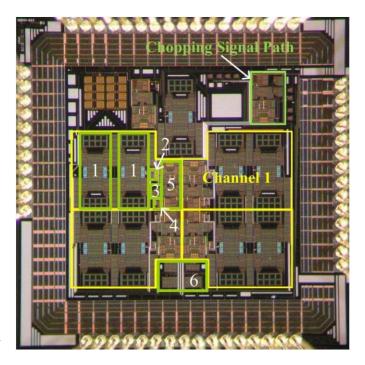

The analog readout was fabricated in a 0.35- $\mu$  mCMOS technology. Fig. 3 shows the chip microphotograph with the various parts identified. A series of electrical tests were first performed to characterize the performance of the circuit (single- and multi-frequency scenarios). Following this, the chip was used with a current driver to perform tetrapolar impedance measurements, as described below. The required input and clock signals were provided from two synchronized TTi TGA12101 signal generators. All output dc voltage measurements were performed with Keithley 2182 Nanovoltmeter. An Agilent Infinii Vision oscilloscope was used to monitor the various voltage signals. External noise or interference sources were not an issue and thus the use of a Faraday cage was not necessary.

Fig. 2. Monte Carlo simulation, including device mismatch and process variations, of a of single channel output. Number of Monte Carlo iterations (N): 500.

Fig. 3. Chip microphotograph indicating each channel in yellow and the chopping signal generation path. 1: filter, 2: demodulation and chopping switches, 3: comparator, 4: gain control switches, 5: variable gain instru-mentation amplifier, 6: current biasing circuitry.

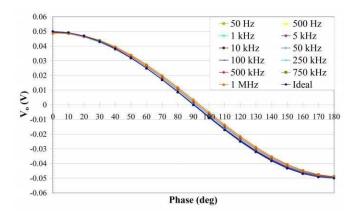

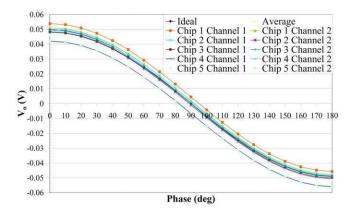

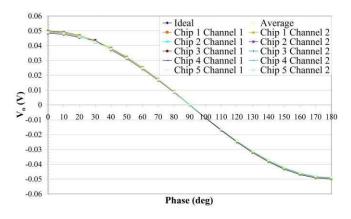

### A. Single-Frequency Measurement

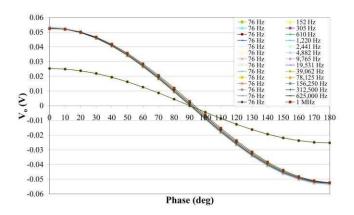

Sinusoidal test signals at various frequencies from 50 Hz to 1 MHz with a peak amplitude of 50 mV, were applied to the chip. The gain of the IA was set to its lowest value of 10 V/V, the output was lowpass filtered, and the phase relationship between input and demodulation signals was varied between  $0^{\circ}$  and  $180^{\circ}$ . Channels 1 and 2 (which provided probing points along the channel to assess their performance) of 5 chips in total were tested and the average results are shown in Fig. 4.

Fig. 4. Measured average dc output following synchronous detection and amplification when varying the phase relationship between input and demodulation signals between  $0^{\circ}$  and  $180^{\circ}$ .

Fig. 5. No chopping: The effect of the random dc offset on the IA on the synchronous detector output from chip-to-chip and channel-to-channel with a  $100~\mathrm{kHz}~50~\mathrm{mV}$  input signal.

Fig. 6. Same as Fig. 5, with chopping at 10 kHz.

Since the signal of interest is at dc, the dc offsets of the IA are important. Fig. 5 shows the effect of the random dc offsets to the system output when the input to the system is a signal of 50 mV amplitude at 100 kHz. Fig. 6 shows how the results are improved giving the correct dc value, when chopping at 10 kHz is performed.

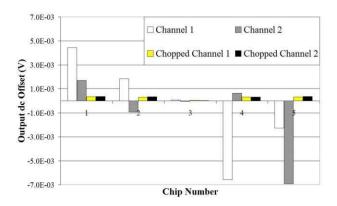

Fig. 7. Measured random dc offset at the outputs of the IA (with gain of 10 V/V, before and after the application of chopping. The data were extracted from Fig. 5 and Fig. 6 for  $\Phi = 90^{\circ}$ .

Fig. 7 shows the value of the IA output dc offset measured before and after the offset

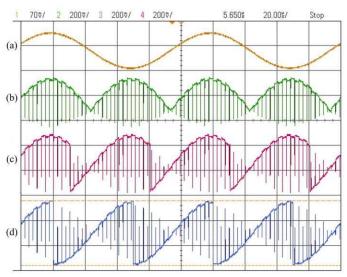

Fig. 8. Waveforms obtained when (a) a sinusoidal input signal with a 50 mV amplitude at 1 kHz is recorded and demodulated by a signal of the same frequency phase shifted by (b)  $0^{\circ}$ ,(c)45° and (d)  $90^{\circ}$ . (b), (c) and (d) are chopped at 10 kHz.

compensation modality used is activated. For example, for channel 2 (no chopping) of chip 5 with an output dc offset of about 7 mV and for a 20  $\mu$  A drive current, using Ohm's law, this corresponds to a 350  $\Omega$  error in the calculation of the real or imaginary parts of the impedance. Fig. 8 presents oscillo-scope waveforms using an input sinusoidal signal of 50 mV at 1 kHz [Fig. 8(a)], a sinusoidal demodulation signal of the same frequency, phase shifted by 0° [Fig. 8(b)], 45° [Fig. 8(c)] and 90° [Fig. 8(d)] and chopped at a frequency of 10 kHz. The effect of chopping can be seen on the signals of Fig. 8(b)-(d). The offset voltage has been modulated to the chopping fre-quency, resulting to the high frequency switching present in these signals [13].

#### B. Multi-Frequency Measurement

For the multi-frequency tests, frequencies from 76 Hz to 1 MHz were used. These frequencies are suitable for neonatal lung function monitoring [18] and cervical cancer

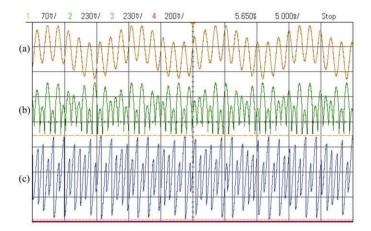

Fig. 9. Multi-frequency measurements. (a) A composite signal comprised of a sinusoid at 76 Hz and 25 mV and a second one at 610 Hz and 53 mV. The recorded signal is demodulated with a 610 Hz square wave at (b)  $0^{\circ}$  and (c)  $90^{\circ}$ . (b) and (c) are chopped at 10 kHz.

Fig. 10. Multi-frequency measurements. Two frequency signals were inputted to the system. The first frequency component was kept at 76 Hz and 25 mV. The second frequency component had constant amplitude of 53 mV and its frequency was varied from 152 Hz to 1 MHz.

detection [24]. Fig. 9 shows waveforms experimentally obtained from the fabricated chip when a multi-sine excitation is introduced to its inputs [Fig. 9(a)]. This is comprised of two frequency components: one at 25 mV, 76 Hz and one at 53 mV, 610 Hz. To illustrate the performance, this is demodulated by a 610 Hz signal 0° [Fig. 9(b)] and 90° [Fig. 9(c)] out of phase and chopped at 10 kHz. Fig. 10 shows the results obtained, as the phase relationship between input and demodulation signals of each frequency component is altered between 0° and 180°. The first frequency component was kept constant at 25 mV, 76 Hz signal, while the second one had a constant 53 mV amplitude but a varying frequency (from 152 Hz to 1 MHz).

### C. RC Circuit Measurement

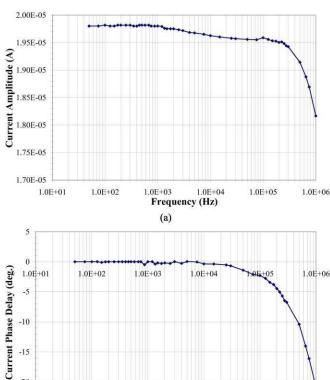

The chip was used with a custom current driver chip (a low current version of [16]) to perform tetrapolar impedance mea-surements. The Bode plots of the magnitude and phase of the output current of the current driver (set to deliver  $20 \mu A$ ) are shown in Fig. 11(a) and (b), respectively. An RC circuit [10] comprised of a 200  $\Omega$  resistor in series with the parallel combination of a 45 nF capacitor and a 5 k $\Omega$ resistor, was

Fig. 11. (a) Magnitude and (b) phase of the output current of the current driver versus frequency.

(b)

Frequency (Hz)

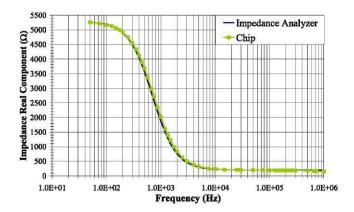

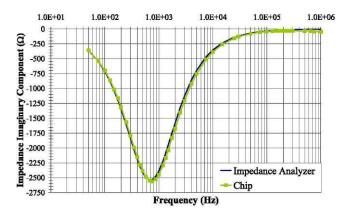

used as the test impedance. A 3  $k\Omega$  sense resistor was placed on each side of this load in order to continuously monitor the current, through an AD8253 IA as in [16]. Synchronization between the injecting and measuring sides is essential in SD and any delays should be minimized or compensated for by adjusting the 0° and 90° demodulation to accommodate the delay. The results of Fig. 11(b) were used in order to adjust the demodulation signal phase, while the results of Fig. 11(a) were subsequently used in order to divide the resulting dc voltage value and obtain the value of the impedance. The real and imaginary parts of the impedance measured using the fabricated chips as a function of frequency, are shown in Figs. 12 and 13, respectively. These are compared with the real and imaginary parts of the same load impedance measured using a Wayne Kerr 6500B impedance analyzer.

#### D. Skin Impedance Measurement

-15

-20

-25

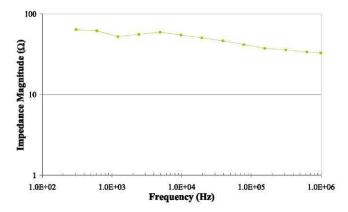

The system was used to measure the impedance of the back of the forearm of a healthy adult volunteer with hairy skin using a tetrapolar arrangement as in [25]. The electrodes used were the Ambu Blue Sensor BRS self-adhesive Ag/AgCl electrodes [26]. The electrode and skin contact size was  $L \chi W = 16 \text{ mm} \chi 19 \text{ mm}$ , with an adhesive area of 269 mm<sup>2</sup>. The adhesive, which comes into contact with the skin, is a solid gel, while the electrode carrier material is carbon-filled polyvinyl chloride. The core of the lead wire is made of carbon which, through a brass/polypropelene connector, is interfaced

Fig. 12. Measured impedance real component versus frequency of the RC circuit characterized.

Fig. 13. Measured impedance imaginary component versus frequency of the RC circuit characterized.

Fig. 14. Skin impedance measurement using the current driver and readout chip with commercially available skin electrodes from Ambu.

with the instrumentation. Fig. 14 shows the magnitude of the impedance as a function of frequency, obtained with the real and imaginary impedance components using the system designed. The results are plotted in a log-log scale to allow a visual comparison with the data presented in [25].

#### IV. DISCUSSION

The measured results obtained from the fabricated analog readout chips show the performance of the system, indicating a good correlation with the theoretical (ideal) performance. Before

TABLE I SUMMARY OF MEASURED PERFORMANCE

| Parameter                     | Value                      |

|-------------------------------|----------------------------|

| Technology                    | 0.35^mCMOS                 |

| Active area                   | 1.525 mm <sup>2</sup>      |

| Supply voltage                | ±2.5 V                     |

| Power consumption per channel | 3.4 mW                     |

| Max operational frequency     | 1 MHz                      |

| IA output dc offset           | 255μν±127μν                |

| Measured impedance range      | $32 \Omega <  Z  > 5.3 kQ$ |

| Mean measurement accuracy     |                            |

| FAIT A IMITA                  | 05.250/                    |

performing tetrapolar measurements, the circuit was characterized with electrical test signals. The ideal response gives a result equal to 50 mV when the phase difference is 0° and 0 V when the phase difference is 90°. The measurement accuracy reduces as the frequency is increased and over the frequency of operation the mean measurement accuracy is about 95% (Table I). This is attributed to comparator non-idealities (such as delay and offset) and residual charge in the choppers (due to charge injection and clock feedthrough).

Fig. 5 clearly indicates the effect of the dc offset on the lock-in amplifier response. In this example a sinusoidal input signal of 50 mV at 100 kHz is applied to the system. After the chopping function is activated and performed with a signal of 10 kHz, the offset is removed and the results are corrected as is evident from Fig. 6. The IA output dc offset voltage is more clearly seen in Fig. 7 where the values obtained from all chips and channels examined are compared with and without chopping. The offset varies from 6.92 mV for the second channel of chip 5, down to 45.3 µV for the second channel of chip 3 without chopping. With chopping it varies from 3.67 mV down to 26.1 µV for the same chips and channels, giving an average value of 255 µY In all cases the offset is reduced. These are not input-referred values. The ability of the system to differentiate between the two frequency components is evident from the results in Fig. 10. The 76 Hz measurement through remains unaffected as the second frequency components is varied. The standard deviation of the 76 Hz data varies between 8.6 µV and 28 µY

According to Fig. 11(a), the output current varies by 1% up to 750 kHz and increases to 2.8% at 1 MHz. Knowledge of the current amplitude is required for calculating the impedance. The response of Fig. 11(b) indicates a phase delay of about 10° at 500 kHz increasing to 21° at 1 MHz. Knowledge of the phase is critical for applying the appropriate demodulation signals in the SD readout.

Having characterized the readout in detail and obtained the current driver characteristics, which are vital for the measurement, the two are combined in order to measure the RC circuit. It is evident from Figs 12 and 13 that theoretical and experimental data are in agreement. The measurement error is less than 1% for frequencies below 350 Hz and less than 4% at 100 kHz. For comparison, the integrated impedance measurement chips in [27] and [28] have an error of 10% at 250 Hz and at 1 kHz, respectively. In addition, both these designs are single-frequency systems. The nonlinearity of the measured impedance over the range of values in Figs 12 and 13 is below 2%.

Finally, the experimental results of Fig. 14 obtained using the fabricated chips and the skin electrodes, are in agreement with the results presented in [25]. Table I summarizes the key features of the chip.

#### V. CONCLUSION

This paper presented an integrated analog readout for multi-frequency bioimpedance measurements. The chip has been assessed in detail with the experimental results demonstrating its single- and multi-frequency performance to a level that, to the authors' knowledge, has not been presented before. The dc offsets of the IA have been minimized through the use of chopping. The paper has identified and compensated for phase errors between the two chopping stages and, more importantly, it has addressed phase issues between the demod-ulation signals and the current driver output, an error that is inherent in common SD topologies but rarely mentioned in the literature. Measurements of the impedance of an RC circuit and tissue have demonstrated good agreement with theoretical and published results. Future work involves the integration of the whole system on a single chip (current driver and readout) with additional features incorporated, such as signal generators and analog-to-digital conversion.

#### REFERENCES

- [1] P.Aberg, I. Nicander, J. Hansson, P. Geladi, U. Holmgren, and S. Ollmar, "Skin cancer identification using multifrequency electrical impedance—A potential screening tool," *IEEE Trans. Biomed. Eng.*, vol. 51, no. 12, pp. 2097-2102, Dec. 2004.

- [2] L.Fabrizi, A.McEwan, T. Oh,E.J. Woo, and D.S.Holder, "A comparison of two EIT systems suitable for imaging impedance changes in epilepsy," *Physiol. Meas.*, vol. 30, no. 6, pp. S103-S120, Jun. 2009.

- [3] U. G. Kyle et al., "Bioelectrical impedance analysis—Part II: Utilization in clinical practice," Clin. Nutrition, vol. 23, no. 6, pp. 1430-1453, Dec. 2004.

- [4] A. D'Amico et al., "Low-voltage low-power integrated analog lock-in amplifier for gas sensor applications," Sens. Actuators B, Chem., vol. 144, no. 2, pp. 400-406, Feb. 2010.

- [5] E. Katz and I. Willner, "Probing biomolecular interactions at conductive and semiconductive surfaces by impedance spectroscopy: Routes to impedimetric immunosensors, DNA-sensors, and enzyme biosensors," *Electroanalysis*, vol. 15, no. 11, pp. 913-947, Jul. 2003.

- [6] D. Holmes and H. Morgan, "Single cell impedance cytometry for iden-tification and counting of CD4 T-cells in human blood using impedance labels," *Anal. Chem.*, vol. 84, no. 4, pp. 1455-1461, Feb. 2010.

- [7] W. R. B. Lionheart, J. Kaipio, and C. N. McLeod, "Generalized optimal current patterns and electrical safety in EIT," *Physiol. Meas.*, vol. 22, no. 1, pp. 85-90, Feb. 2001.

- [8] B. Sanchez, G. Vanderteen, R. Bragos, and J. Schoukens, "Basics of broadband impedance spectroscopy measurements using periodic exci-tations," *Meas. Sci. Technol.*, vol. 23, no. 10, pp. 105501-1-105501-14, Oct. 2012.

- [9] A. Yufera and A. Rueda, "Design of a CMOS closed-loop system with applications to bio-impedance measurements," *Microelectron. J.*, vol. 41, no. 4, pp. 231-239, Apr. 2010.

- [10] P. Kassanos, I. F. Triantis, and A. Demosthenous, "A CMOS magnitude/ phase measurement chip for impedance spectroscopy," *IEEE Sensors J.*, vol. 13, no. 6, pp. 2229-2236, Jun. 2013.

- [11] C. S. Koukourlis, V. K. Trigonidis, and J. N. Sahalos, "Differential synchronous demodulation for small-signal amplitude estimation," *IEEE Trans. Instrum. Meas.*, vol. 42, no. 5, pp. 926-931, Oct. 1993.

- [12] M. Min, T. Parve, A. Ronk, P. Annus, and T. Paavle, "Synchronous sampling and demodulation in an instrument for multifrequency bioim-pedance measurement," *IEEE Trans. Intrum. Meas.*, vol. 56, no. 4, pp. 1365-1372, Aug. 2007.

- [13] M. Rahal and A. Demosthenous, "A synchronous chopping demodulator and implementation for high-frequency inductive position sensors," *IEEE Trans. Instrum. Meas.*, vol. 58, no. 10, pp. 3693-3701, Oct. 2009.

- [14] I. F. Triantis, A. Demosthenous, M. Rahal, H. Hong, and R. Bayford, "A multi-frequency bioimpedance measurement ASIC for electrical impedance tomography," in *Proc. ESSCIRC*, Helsinki, Finland, Sep. 2011, pp. 331-334.

- [15] R. Pallas-Areny and J. G. Webster, Analog Signal Processing. New York, NY, USA: Wiley, 1999, pp. 259-269.

- [16] L. Constantinou, I. F. Triantis, R. Bayford, and A. Demosthenous, "High-power CMOS current driver with accurate transconductance for electrical impedance tomography," *IEEE Trans. Biomed. Circuits Syst.*, doi: 10.1109/TBCAS.2013.2285481.

- [17] H. Hong, M. Rahal, A. Demosthenous, and R. H. Bayford, "Comparison of a new integrated current source with the modified Howland circuit for EIT applications," *Physiol. Meas.*, vol. 30, no. 10, pp. 999-1007, Oct. 2009.

- [18] B. H. Brown, R. A. Primhak, R. H. Smallwood, P. Milnes, A. J. Narracott, and M. J. Jackson, "Neonatal lungs: Can absolute lung resistivity be determined non-invasively?" *Med. Biol. Eng. Comput.*, vol. 40, no. 4, pp. 388-394, Jul. 2002.

- [19] J. K. Seo, J. Lee, S. W. Kim, H. Zribi, and E. J. Woo, "Frequency-difference electrical impedance tomography (fdEIT): Algorithm devel-opment and feasibility study," *Physiol. Meas.*, vol. 29, no. 8, pp. 929-944, Aug. 2008.

- [20] R. Casanella, O. Casas, and R. Pallas-Areny, "Differential synchronous demodulator for modulating sensors and impedance measurements," *Meas. Sci. Technol.*, vol. 16, no. 8, pp. 1637-1643, Jul. 2005.

- [21] A. Worapishet, A. Demosthenous, and X. Liu, "A CMOS instrumentation amplifier with 90-dB CMRR at 2-MHz using capacitive neutraliza-tion: Analysis, design considerations, and implementation," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 4, pp. 699-710, Apr. 2011.

- [22] C. C. Enz and G. C. Temes, "Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization," *Proc. IEEE*, vol. 84, no. 11, pp. 1584-1614, Nov. 1996.

- [23] J. F. Witte, K. A. A. Makinwa, and J. H. Huijsing, *Dynamic Offset Compensated CMOS Amplifiers*. Dordrecht, The Netherlands: Springer-Verlag, 2009, pp. 27-40.

- [24] Zilico Ltd., Sheffield, U.K. (2013). ZedScanI [Online]. Available: http://www.zilico.co.uk/products/zedscan.html [25] M. Rahal, J. M. Khor, A. Demosthenous. A. Tizzard, and R. H. Bayford,

- "A comparison study of electrodes for neonate electrical impedance tomography," *Physiol. Meas.*, vol. 30, no. 6, pp. S73-S84, Jun. 2009.

- [26] Ambu A/S, Ballerup, Denmark. (2013). Ambu Blue Sensor BRS Datasheet [Online]. Available: <a href="http://www.ambu.com/corp/products/">http://www.ambu.com/corp/products/</a> area\_of\_interests/emergency\_room/product/ambu%C2%AE\_bluesensor\_ brs-prod119.aspx

- [27] M. Guermandi, R. Cardu, E. Franchi, and R. Guerrieri, "Active elec-trode IC combining EEG, electrical impedance tomography, continuous contact impedance measurement and power supply on a single wire," in *Proc. ESSCIRC*, Helsinki, Finland, Sep. 2011, pp. 335-338.

- [28] A. Yiifera, A. Rueda, J. M. Mufloz, R. Doldan, G. Leger, and E. O. Rodriguez-Villegas, "A tissue impedance measurement chip for myocardial ischemia detection," *IEEETrans. Circuits Syst. I, Reg. Papers*, vol. 52, no. 12, pp. 2620-2628, Dec. 2005.

Panagiotis Kassanos (S'08-M'11) was born in Athens, Greece, in 1983. He received the M.Eng. and Ph.D. degrees in electronic and electrical engi-neering from University College London (UCL), London, U.K., in 2006 and 2012, respectively.

He held a Post-Doctoral EPSRC Ph.D. + Research Fellowship from 2010 to 2011 and was a Research Associate from 2011 to 2013 with the Analog and Biomedical Electronics Group, Department of Electronic and Electrical Engineering, UCL. Since 2013, he has been an Honorary Research Associate with the Biomedical Engineering Research Group, Department of Electrical and Electronic Engineering, City University,

London. He is currently a Research Associate with the Hamlyn Centre, Institute of Global Health Innovation, Imperial College, London. His current research interests include analog and mixed-signal integrated circuits for biomedical, sensor and signal processing applications, and sensor design.

Loucas Constantinou (S'10) was born in Limassol, Cyprus, in 1986. He received the M.Eng. (Hons.) degree in biomedical engineering from the Imperial College, London, U.K., in 2010. He then joined the Analog and Biomedical Electronics Group with the Department of Electronic and Electrical Engi-neering, University College London (UCL). He is currently pursuing the Ph.D. degree in bioimpedance spectroscopy. He was awarded a UCL studentship funded by the Engineering and Physical Sciences Research Council.

His research interests are in the area of analog integrated circuit design for biomedical applications, wideband ac current

drivers, and electrical impedance tomography.

**Iasonas F. Triantis** (M'02) was born in Geneva, Switzerland, in 1976. He received the M.Eng. degree in electronic engineering from MIST, Manchester, U.K., in 2000, and the Ph.D. degree in electronic engineering from the University College London

(UCL), London, U.K.

He was a Research Assistant at UCL until 2005, where he was involved in implantable neuropros-thetics and neural interfacing. He was a Research Associate with the Imperial College London, Lon-don, until 2010, where he was involved in neural recording and stimulation chips, and researched

alternative neural interfacing methods that could be used in both the peripheral and the central nervous system. He then returned to UCL as a Senior Research Associate to work on electrical impedance tomography microelectronic systems for neonatal lung monitoring. Since 2012, he has been a Lecturer with the Biomedical Engineering Research Group, School of Engineering and Mathematical Sci-ences, City University, London, specializing in instrumentation and sensors for biointerfacing research. He has authored ten journal and 29 conference publications, and three book chapters. He holds three patents and an IEEE newsletter.

Andreas Demosthenous (S'94-M'99-SM'05) received the B.Eng. degree in electrical and electronic engineering from the University of Leicester, Leicester, U.K., the M.Sc. degree in telecommunications technology from Aston University, Birmingham, U.K., and the Ph.D. degree in electronic and electrical engineering from the University College London (UCL), London, U.K.,

in 1992, 1994, and 1998, respectively.

He was a Post-Doctoral Research Fellow with the Department of Electronic and Electrical Engineering, UCL, from 1998 to 2000. He became an Academic Faculty Member

in 2000, and is currently a Professor leading the Analog and Biomedical Electronics Group. He is the Director of Research in his Department. He has numerous collaborations for interdisciplinary research. His current research interests include analog and mixed-signal integrated circuits for biomedical, sensor, and signal processing applications. He has authored over 190 articles in journals and international conference proceedings in these research areas. He holds several patents. He has graduated 15 Ph.D. students, and has supervised many post-doctoral research staff members.

Dr. Demosthenous is the Deputy Editor-in-Chief of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS II: EXPRESS BRIEFS for 2014 to 2015, and was an Associate Editor of the same journal from 2006 to 2007. He is an Associate Editor of the IEEE TRANSACTIONS ON BIOMEDICAL CIRCUITS AND SYSTEMS, the IEEE CIRCUITS AND SYSTEMS NEWSLETTER, and an International Advisory Board Member of *Physiological Measurement*, Institute of Physics. He was an Associate Editor of the IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS I: REGULAR PAPERS from 2008 to 2012. He is a member of various professional committees, including the Analog Signal Processing Technical Committee and the Biomedical Circuits and Systems Technical Committee of the IEEE Circuits and Systems Society. He is a member of the Technical Program Committee of various IEEE conferences, including the European Solid-State Circuits Conference and the International Conference on Very Large Scale Integration of System-on-Chip. He was on the organizing committee of the 2013 IEEE Biomedical Circuits and Systems Conference. He is a fellow of the Institution of Engineering and Technology and a Chartered Engineer.