# **City Research Online**

## City, University of London Institutional Repository

**Citation**: Xu, Quan (2016). Data reliability and error correction for NAND Flash Memory System. (Unpublished Doctoral thesis, City University London)

This is the accepted version of the paper.

This version of the publication may differ from the final published version.

Permanent repository link: https://openaccess.city.ac.uk/id/eprint/15120/

Link to published version:

**Copyright:** City Research Online aims to make research outputs of City, University of London available to a wider audience. Copyright and Moral Rights remain with the author(s) and/or copyright holders. URLs from City Research Online may be freely distributed and linked to.

**Reuse:** Copies of full items can be used for personal research or study, educational, or not-for-profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

# Data Reliability and Error Correction for NAND Flash Memory System

### Quan Xu

School of Mathematics, Computer Science & Engineering City University London

This dissertation is submitted for the degree of Doctor of Philosophy

June 2016

### Declaration

This thesis is presented in fulfilment of the requirement for the degree of Doctor of Philosophy. The research reported in this doctoral thesis has been carried out at the City University London. I declare that except where specific reference is made to the work of others, the contents of this dissertation are original and have not been submitted in whole or in part for consideration for any other degree or qualification in this, or any other university. This dissertation is my own work and contains nothing which is the outcome of work done in collaboration with others, except as specified in the text and Acknowledgements.

Quan Xu June 2016

### Acknowledgements

I take this opportunity to express my sincere gratitude to my advisor, Professor Tom Chen, for his continuing guidance, support and encouragement. His enthusiasm and expertise in the area of signal processing, error correction coding and probability theory help me better understand the subtle facets of this work. His rigorous attitude toward science stimulates me throughout the writing of thesis.

I also thank my officemates, Mr Pu Gong, Mr Tareq Alalyani and Dr Jorge Blasco. Their advice and ideas help me walk forward and are very important to my research. Working with these colleagues has not only been a good learning experience, but also a great pleasure. In addition, I acknowledge iStorage Limited and Mr John Michael for his great support to my research project in flash channel modelling.

I would like to thank the coauthors of my publications for their collaborations. Special thanks to Dr Yupeng Hu at the Hunan University, and Dr Shancang Li at the Edinburgh Napier University for their help in applying LDPC coding to the flash storage error correction. I also acknowledge Qiang Liao, Jian Yu in Initio Corporation for their valuable advice on the implementation of ECC decoder and the data pattern processing schemes.

I am sincerely grateful to my parents and my fiancée for always being supportive and encouraging in my pursuit of academic excellence. Without them, I would not ever have completed this dissertation.

#### Abstract

NAND flash memory has been widely used for data storage due to its high density, high throughput, and low power. However, as the flash memory scales to smaller process technologies and stores more bits per cell, its reliability is decreasing. The error correction coding can be used to significantly improve the data reliability; nevertheless, the advanced ECCs such as low-density parity-check (LDPC) codes generally demand soft-decisions while NAND flash memory channel provides hard-decisions only. Extracting the soft information requires the accurate characterization of flash memory channel and the effective design of coding schemes.

To this end, we have presented a novel LDPC-TCM coding scheme for the Multilevel Cell (MLC) flash memories. The a posteriori TCM decoding algorithm is used in the scheme to generate soft information, which is fed to the LDPC decoder for further correction of data bits. It has been demonstrated that the proposed scheme can achieve higher error correction performance than the traditional hard-decisions based flash coding algorithms, and is feasible in the design practice. Further with the LDPC-TCM, we believe it is important to characterize the flash memory channel and investigate a method to calculate the soft decision for each bit, with the available channel outputs. We studied the various noises and interferences occurring in the memory channel and mathematically formulated the probability density function of the overall noise distribution. Based on the results we derived the final distribution for the cell threshold voltages, which can be used to instruct the calculation of soft decisions. The discoveries on the theoretical level have been demonstrated to be consistent with the real channel behaviours. The channel characterization and model provided in this dissertation can enable more design of soft-decisions based ECCs for future NAND flash memories. The data pattern processing algorithm deals with the write patterns and targets to lower the proportion of patterns that would introduce data errors. On the other hand, the voltages applied to the memory cells charges the MOSFET capacitances frequently on programming these data patterns, leading to the power problem. The high energy consumption and current spikes also cause reliability issue to the data stored in the flash memory. This dissertation proposes a write pattern formatting algorithm (WPFA) attempting to solve the two problems together. We have designed and implemented the algorithm and evaluated its performance through both the software simulations and hardware synthesis.

## **Table of contents**

| List of figures |                    |                                                                                   |                                             |      |  |  |  |

|-----------------|--------------------|-----------------------------------------------------------------------------------|---------------------------------------------|------|--|--|--|

| Li              | List of tables xii |                                                                                   |                                             |      |  |  |  |

| Li              | st of A            | t of Abbreviations xiii<br>t of Notations xiv<br>Introduction 1<br>1.1 Motivation |                                             |      |  |  |  |

| Li              | st of I            | Notatio                                                                           | ns                                          | xiv  |  |  |  |

| 1               | Intr               | oductio                                                                           | n                                           | 1    |  |  |  |

|                 | 1.1                | Motiva                                                                            | ation                                       | 3    |  |  |  |

|                 | 1.2                | Goals                                                                             |                                             | . 8  |  |  |  |

|                 | 1.3                | Thesis                                                                            | Contribution                                | . 9  |  |  |  |

|                 | 1.4                | Thesis                                                                            | Outline                                     | . 12 |  |  |  |

| 2               | Bac                | kgroun                                                                            | d                                           | 14   |  |  |  |

|                 | 2.1                | Basics                                                                            | s of NAND Flash Memory                      | . 14 |  |  |  |

|                 |                    | 2.1.1                                                                             | NAND Device Organization                    | . 15 |  |  |  |

|                 |                    | 2.1.2                                                                             | NAND Cell Architecture and Basic Operations | . 16 |  |  |  |

|                 |                    | 2.1.3                                                                             | Planar and 3D NAND Flash Memory             | . 21 |  |  |  |

|                 | 2.2                | Data F                                                                            | Reliability Issues                          | . 23 |  |  |  |

|                 |                    | 2.2.1                                                                             | Reliability at Physical Level               | . 23 |  |  |  |

|                 |                    | 2.2.2                                                                             | Noises in NAND Flash Memory                 | . 24 |  |  |  |

|                 |                    | 2.2.3                                                                             | Error Correction Codes for Flash Memories   | . 30 |  |  |  |

|                 | 2.3                | NANI                                                                              | D-based Memory System Overview              | . 32 |  |  |  |

| 2.4                                                                         | Summ                                                                                               | ary and Challenges                                                                                                                                                                                                        | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wri                                                                         | te Patte                                                                                           | rn Formatting Algorithm and Implementation                                                                                                                                                                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.1                                                                         | Proble                                                                                             | m Description                                                                                                                                                                                                             | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.2                                                                         | Relate                                                                                             | d Work                                                                                                                                                                                                                    | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.3                                                                         | Write                                                                                              | Pattern Formatting Algorithm                                                                                                                                                                                              | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.4                                                                         | Perfor                                                                                             | mance Evaluation                                                                                                                                                                                                          | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | 3.4.1                                                                                              | Maximum Length of Column Stripe Patterns                                                                                                                                                                                  | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | 3.4.2                                                                                              | Average Program Current                                                                                                                                                                                                   | 48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | 3.4.3                                                                                              | Proportion of the Highest $V_{th}$ State                                                                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | 3.4.4                                                                                              | Overhead of NAND Cell Area                                                                                                                                                                                                | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.5                                                                         | Hardw                                                                                              | are Design and Implementation Complexity                                                                                                                                                                                  | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | 3.5.1                                                                                              | Hardware Implementation of WPFA Encoder and Decoder                                                                                                                                                                       | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | 3.5.2                                                                                              | Analysis of Implementation Complexity                                                                                                                                                                                     | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 3.6                                                                         | Summ                                                                                               | ary and Challenges                                                                                                                                                                                                        | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             |                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C                                                                           |                                                                                                    |                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                             |                                                                                                    | ed LDPC-TCM Error Correction Coding                                                                                                                                                                                       | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.1                                                                         |                                                                                                    | ed LDPC-TCM Error Correction Coding                                                                                                                                                                                       | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | Proble                                                                                             | 0                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 4.1                                                                         | Proble                                                                                             | m Description                                                                                                                                                                                                             | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 4.1                                                                         | Proble<br>Backg                                                                                    | m Description                                                                                                                                                                                                             | 65<br>67<br>68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1                                                                         | Proble<br>Backg<br>4.2.1                                                                           | m Description                                                                                                                                                                                                             | 65<br>67<br>68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1                                                                         | Proble<br>Backgr<br>4.2.1<br>4.2.2<br>4.2.3                                                        | m Description                                                                                                                                                                                                             | 65<br>67<br>68<br>74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4.1<br>4.2                                                                  | Proble<br>Backgr<br>4.2.1<br>4.2.2<br>4.2.3                                                        | m Description                                                                                                                                                                                                             | 65<br>67<br>68<br>74<br>77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 4.1<br>4.2                                                                  | Proble<br>Backg<br>4.2.1<br>4.2.2<br>4.2.3<br>Concar                                               | m Description                                                                                                                                                                                                             | 65<br>67<br>68<br>74<br>77<br>79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.1<br>4.2                                                                  | Proble<br>Backgr<br>4.2.1<br>4.2.2<br>4.2.3<br>Concar<br>4.3.1                                     | m Description                                                                                                                                                                                                             | <ul> <li>65</li> <li>67</li> <li>68</li> <li>74</li> <li>77</li> <li>79</li> <li>79</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4.1<br>4.2                                                                  | Proble<br>Backg<br>4.2.1<br>4.2.2<br>4.2.3<br>Concar<br>4.3.1<br>4.3.2<br>4.3.3                    | m Description                                                                                                                                                                                                             | <ul> <li>65</li> <li>67</li> <li>68</li> <li>74</li> <li>77</li> <li>79</li> <li>79</li> <li>82</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                               | Proble<br>Backg<br>4.2.1<br>4.2.2<br>4.2.3<br>Concar<br>4.3.1<br>4.3.2<br>4.3.3<br>Perform         | m Description                                                                                                                                                                                                             | <ul> <li>65</li> <li>67</li> <li>68</li> <li>74</li> <li>77</li> <li>79</li> <li>79</li> <li>82</li> <li>84</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul> | Proble<br>Backg<br>4.2.1<br>4.2.2<br>4.2.3<br>Concar<br>4.3.1<br>4.3.2<br>4.3.3<br>Perform<br>Summ | m Description                                                                                                                                                                                                             | <ul> <li>65</li> <li>67</li> <li>68</li> <li>74</li> <li>77</li> <li>79</li> <li>79</li> <li>82</li> <li>84</li> <li>86</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                             | Wri<br>3.1<br>3.2<br>3.3<br>3.4                                                                    | Write Patter         3.1       Proble         3.2       Relater         3.3       Write I         3.4       Perform         3.4.1       3.4.2         3.4.3       3.4.3         3.5       Hardw         3.5.1       3.5.2 | Write Pattern Formatting Algorithm and Implementation         3.1       Problem Description         3.2       Related Work         3.3       Write Pattern Formatting Algorithm         3.4       Performance Evaluation         3.4.1       Maximum Length of Column Stripe Patterns         3.4.2       Average Program Current         3.4.3       Proportion of the Highest V <sub>th</sub> State         3.4.4       Overhead of NAND Cell Area         3.5       Hardware Design and Implementation Complexity         3.5.1       Hardware Implementation Complexity |

|    | 5.2     | Backg   | round                                                      | . 100 |

|----|---------|---------|------------------------------------------------------------|-------|

|    |         | 5.2.1   | Equivalent Channel Model Incorporated with Major Threshold |       |

|    |         |         | Voltage Distortions                                        | . 100 |

|    |         | 5.2.2   | Characteristic Functions of Random Variables               | . 107 |

|    |         | 5.2.3   | Related Work                                               | . 110 |

|    | 5.3     | Charac  | cterisation of NAND Flash Memory Channel                   | . 111 |

|    |         | 5.3.1   | Overall Distribution of the Noises and Distortions         | . 112 |

|    |         | 5.3.2   | Cell Threshold Voltage Distributions                       | . 124 |

|    | 5.4     | Calcul  | ation of Soft Decisions                                    | . 127 |

|    | 5.5     | Summ    | ary and Challenges                                         | . 129 |

| 6  | Con     | clusion | s and Future Work                                          | 131   |

|    | 6.1     | Thesis  | Conclusion                                                 | . 131 |

|    | 6.2     | Direct  | ions for Future Work                                       | . 133 |

| Re | eferen  | ices    |                                                            | 136   |

| Li | st of l | Related | Publications                                               | 142   |

# List of figures

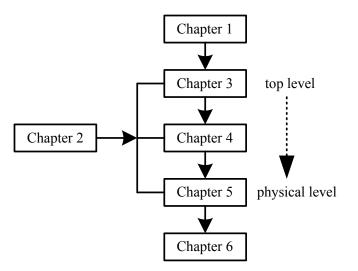

| 1.1  | Overview of the thesis organization.                                  | 12 |

|------|-----------------------------------------------------------------------|----|

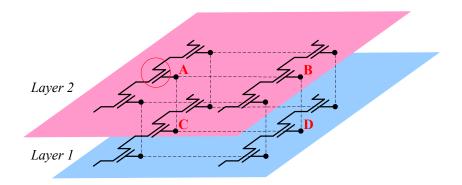

| 2.1  | NAND flash memory array structure                                     | 16 |

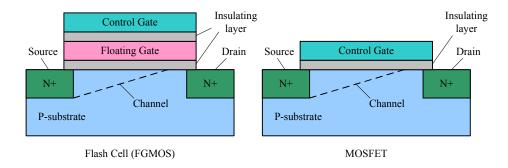

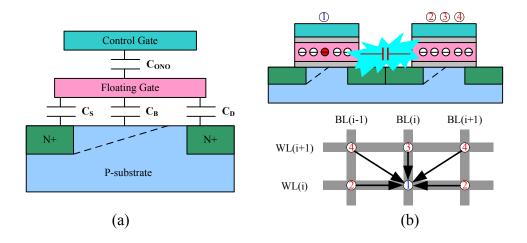

| 2.2  | Flash memory cell vs. MOSFET                                          | 17 |

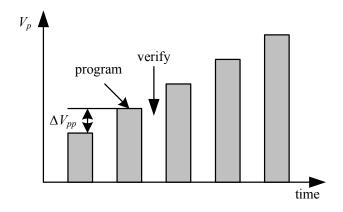

| 2.3  | Control-gate voltage in program operation                             | 19 |

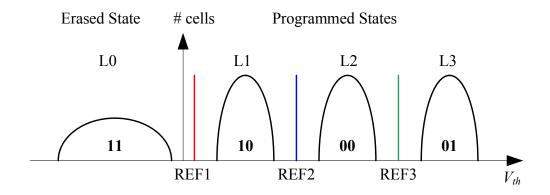

| 2.4  | Read reference voltages for 4-level MLC                               | 20 |

| 2.5  | A Typical structure of VG flash memory                                | 22 |

| 2.6  | Capacitors involved in the NAND flash memory channel                  | 25 |

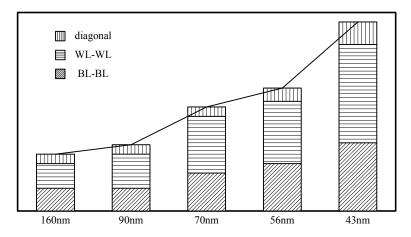

| 2.7  | Cell to cell coupling trend.                                          | 26 |

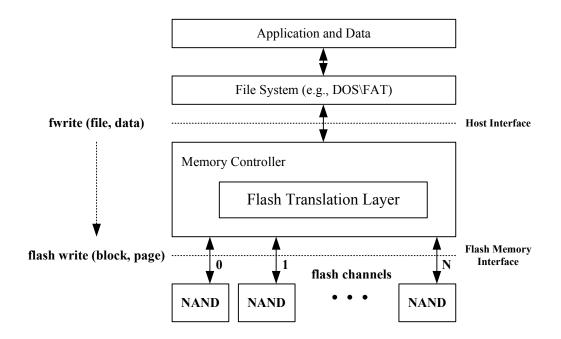

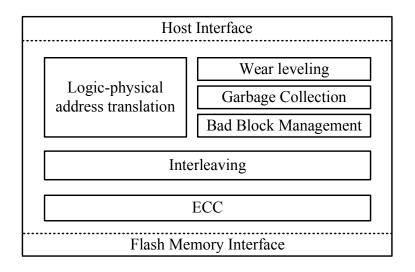

| 2.8  | Functional representation of a NAND-based memory system               | 33 |

| 3.1  | Functions implemented in the flash translation layer.                 | 36 |

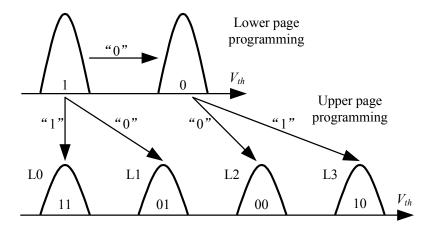

| 3.2  | Example of multipage programming for 2 bits/cell NAND flash memory.   | 38 |

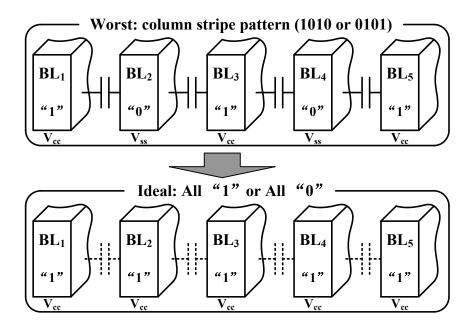

| 3.3  | Operation of pre-charging under different programming data patterns   | 40 |

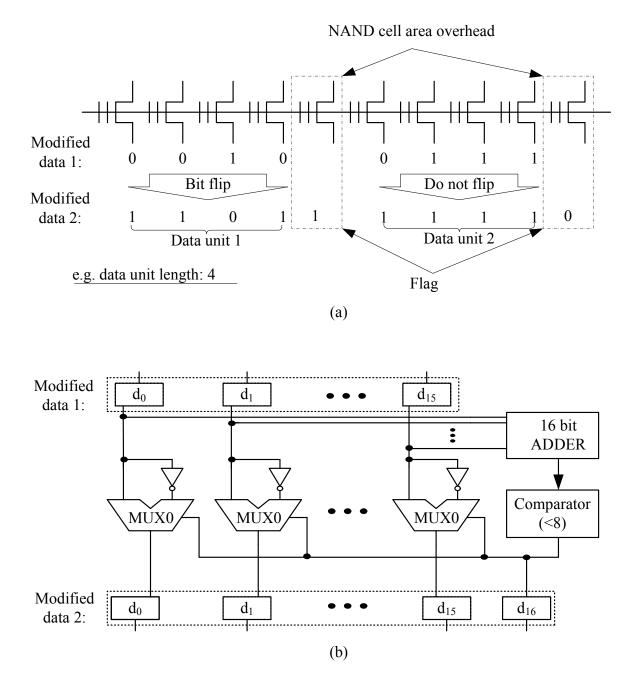

| 3.4  | (a) Algorithm of the asymmetric coding. (b) Schematic circuit diagram |    |

|      | of the asymmetric coding encoder                                      | 41 |

| 3.5  | Example of SPEA.                                                      | 43 |

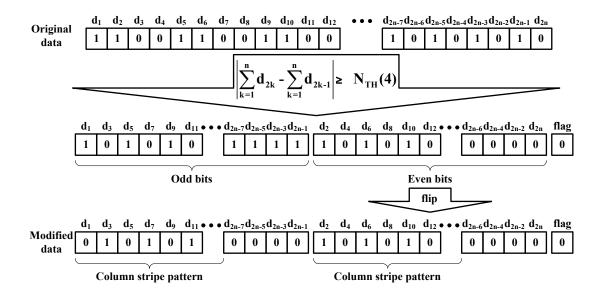

| 3.6  | WPFA: lower page data.                                                | 44 |

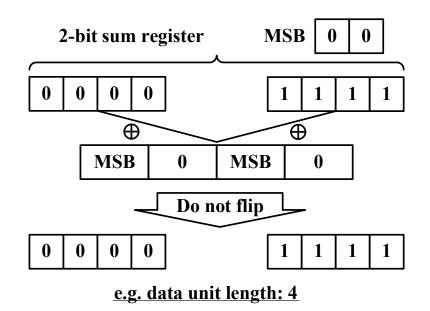

| 3.7  | Analysis of two specific data patterns                                | 45 |

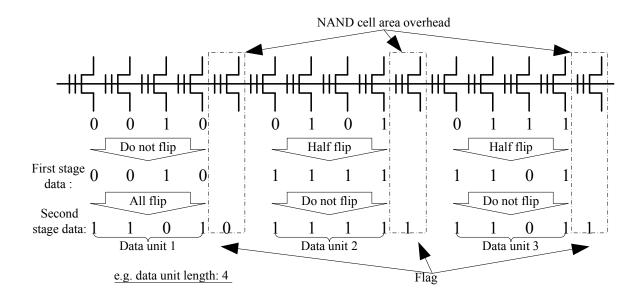

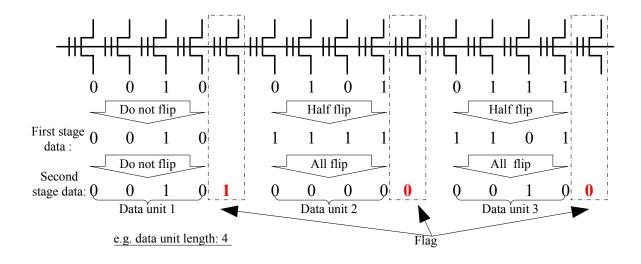

| 3.8  | WPFA: upper page data.                                                | 47 |

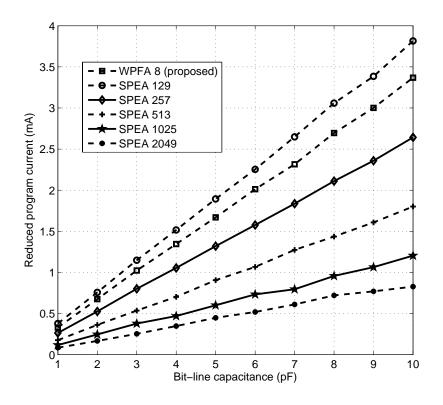

| 3.9  | Reduced program current over the system without power saving scheme   | 50 |

| 3.10 | Data patterns before and after WPFA processing                        | 51 |

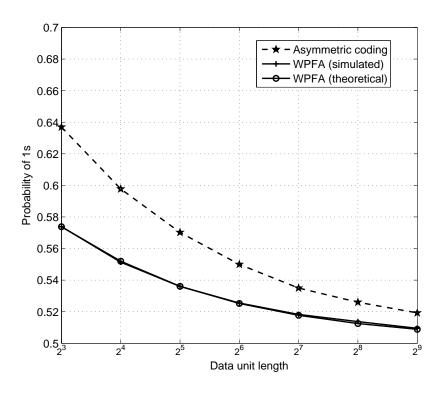

| 3.11 | Simulation results of probabilities of "1"s in Tanakamaru's and the        |    |

|------|----------------------------------------------------------------------------|----|

|      | proposed schemes.                                                          | 53 |

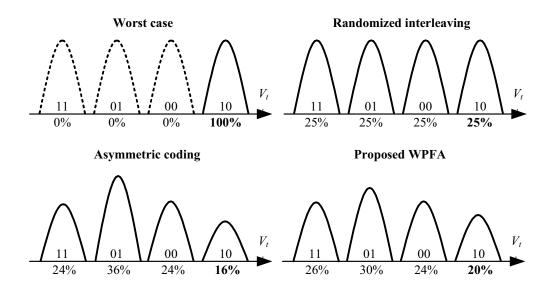

| 3.12 | $V_{th}$ distributions of the worst case, randomized interleaving, and the |    |

|      | proposed algorithm.                                                        | 54 |

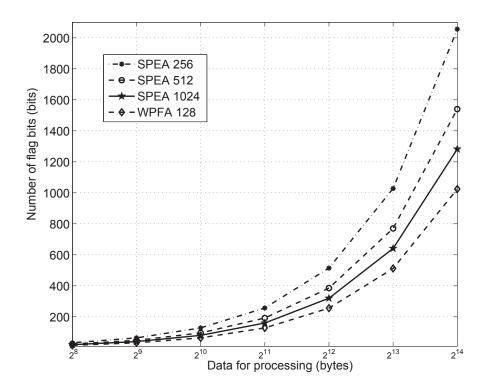

| 3.13 | The number of flag bits required for WPFA and Tanakamaru's algorithm.      | 55 |

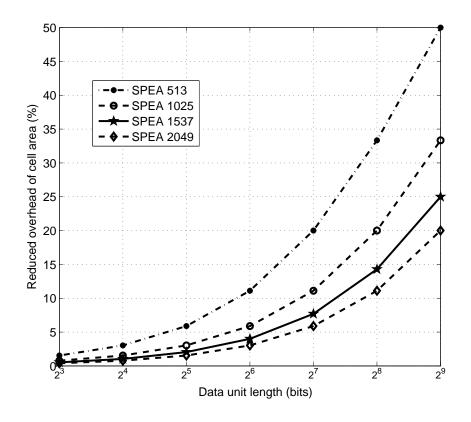

| 3.14 | The reduced NAND cell area overhead to Tanakamaru's design                 | 56 |

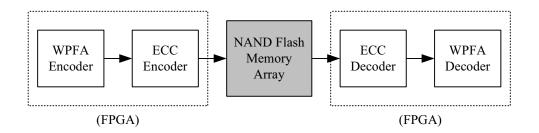

| 3.15 | Framework of coding mechanism in SSDs                                      | 57 |

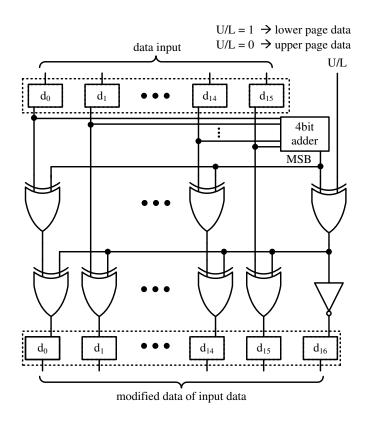

| 3.16 | Circuit schematic of the joint lower/upper pages WPFA encoder              | 59 |

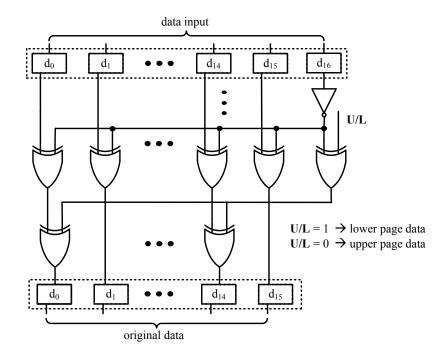

| 3.17 | Circuit schematic of the joint lower/upper pages WPFA decoder              | 59 |

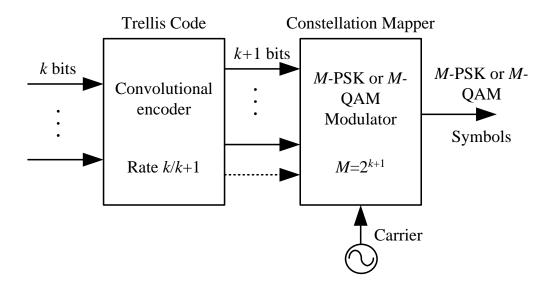

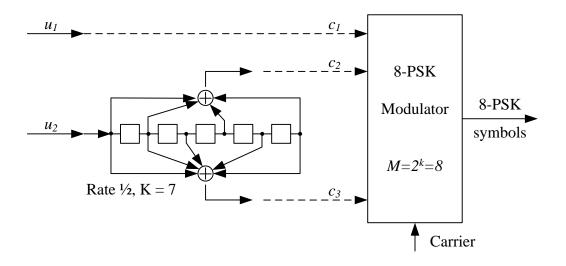

| 4.1  | A general trellis coded modulation                                         | 69 |

| 4.2  |                                                                            |    |

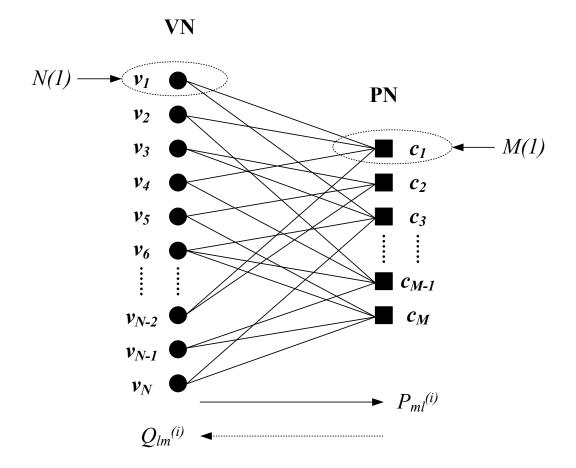

| 4.3  | Tanner graph representation for an LDPC code                               | 75 |

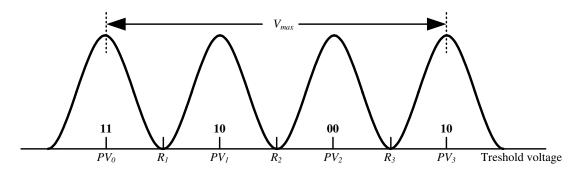

| 4.4  | The approximate flash memory cell threshold voltage distribution model.    | 80 |

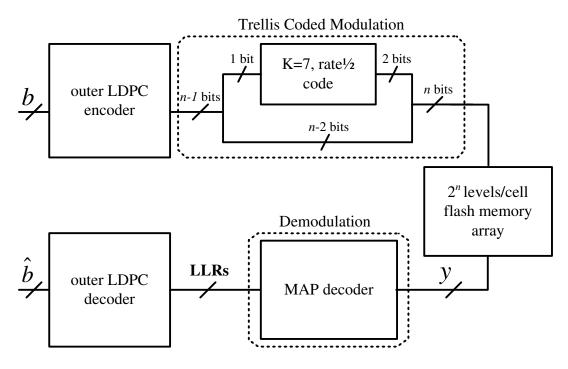

| 4.5  | Block diagram of TCM LDPC coding system.                                   | 81 |

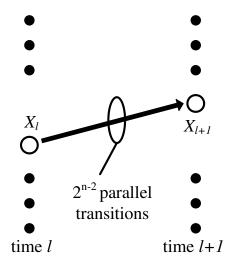

| 4.6  | State transitions in pragmatic TCM                                         | 83 |

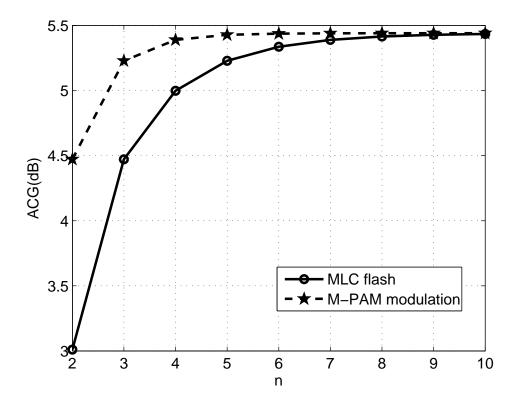

| 4.7  | Asymptotic coding gain of TCM for MLC flash memories and M-PAM             |    |

|      | modulation.                                                                | 87 |

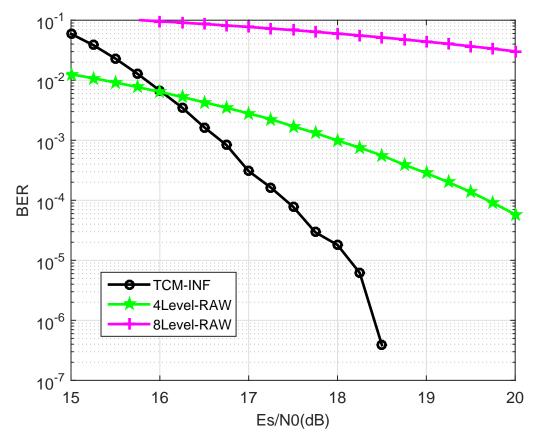

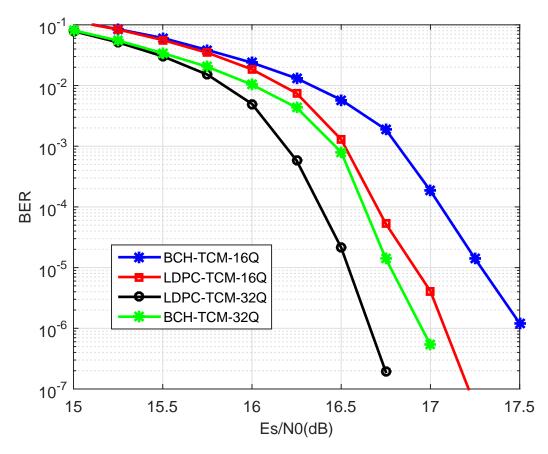

| 4.8  | Performance comparisons for the raw BERs of 4 levels, 8 levels MLC         |    |

|      | and TCM without quantization                                               | 89 |

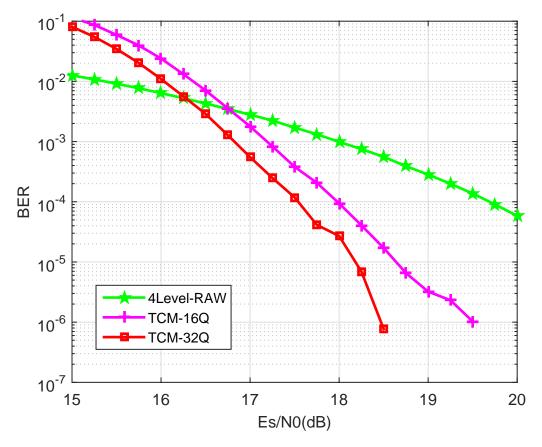

| 4.9  | Performance comparisons of the raw BER of 4 levels and the TCM with        |    |

|      | quantization                                                               | 90 |

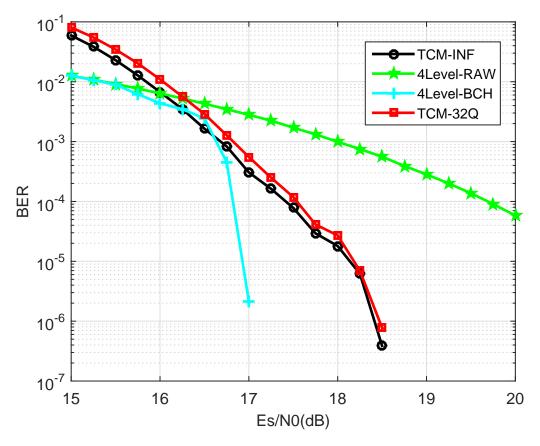

| 4.10 | Performance comparisons of the raw BER of 4 levels, the BCH coding         |    |

|      | and the TCM for NAND flash memories                                        | 91 |

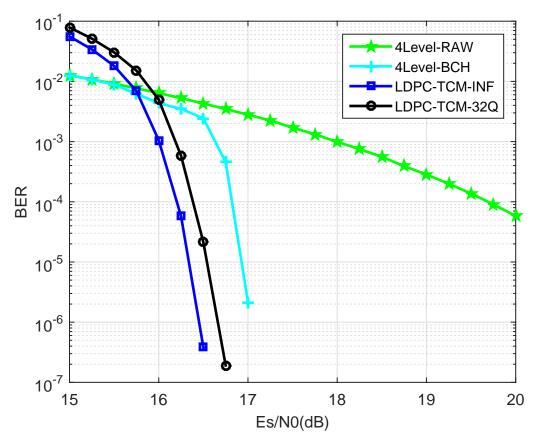

| 4.11 | Performance comparisons of the raw BER of 4 levels, the BCH coding         |    |

|      | and the proposed LDPC-TCM coding.                                          | 92 |

| 4.12 | Performance comparisons of the raw BER of 4 levels, the BCH coding         |    |

|      | and the proposed LDPC-TCM coding.                                          | 94 |

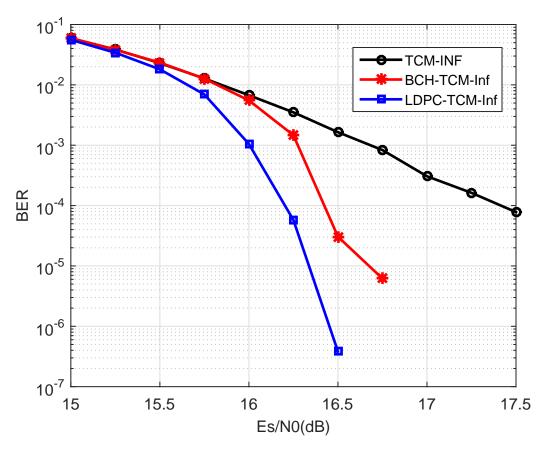

| 4.13 | Performance comparisons of the BCH coding and the proposed LDPC-           |    |

|      | TCM coding with quantized flash channel outputs.                           | 95 |

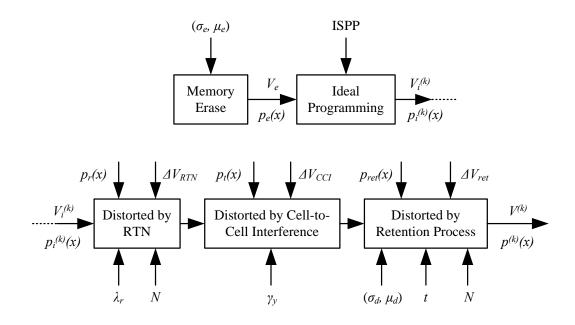

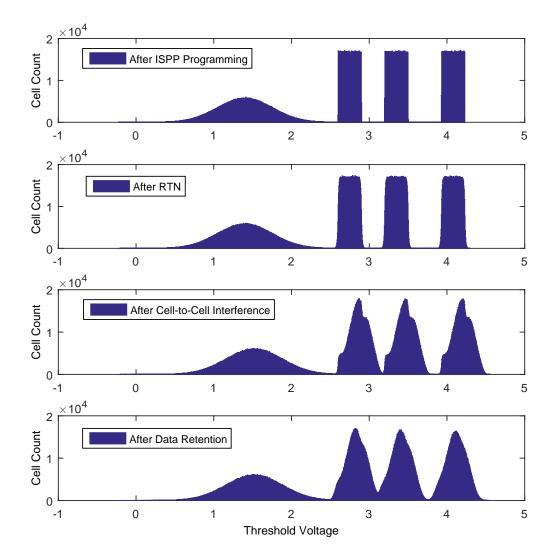

| 5.1 | Approximate NAND flash memory device model to incorporate major          |

|-----|--------------------------------------------------------------------------|

|     | threshold voltage distortion sources                                     |

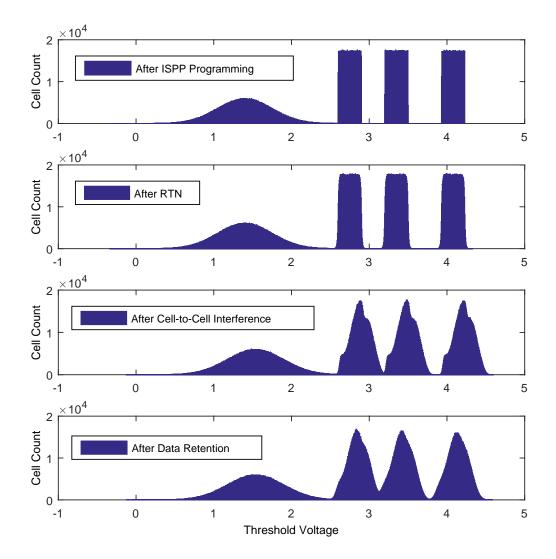

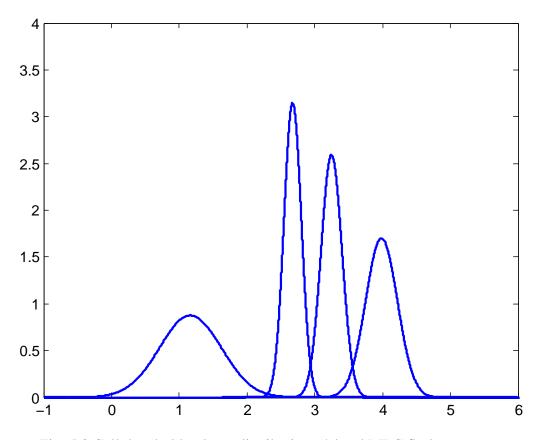

| 5.2 | Simulation of threshold-voltage distribution after 1K P/E Cycling and 1  |

|     | month retention: memory cell suffers CCI from vertical and diagonal      |

|     | neighbouring cells                                                       |

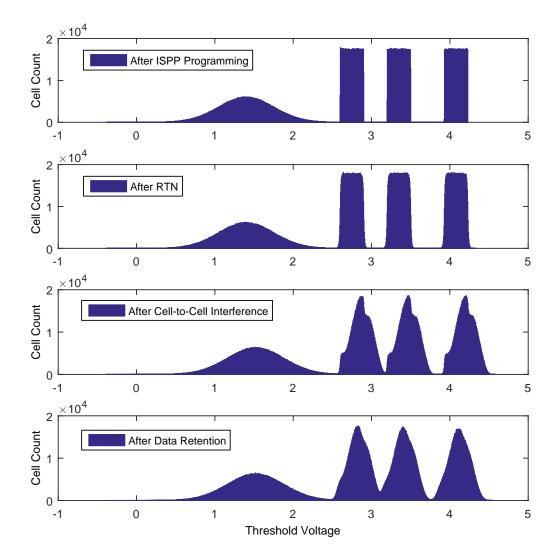

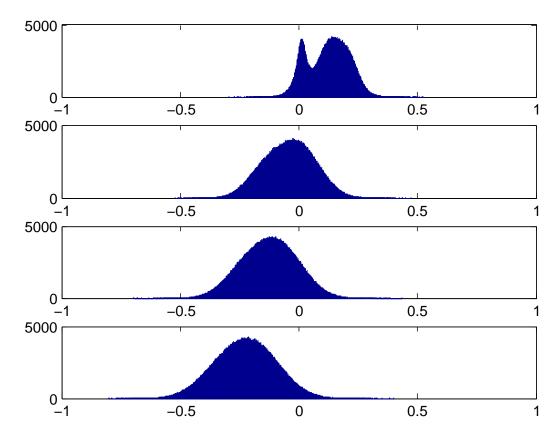

| 5.3 | Simulation of memory threshold-voltage distribution after 1K P/E Cy-     |

|     | cles and 1 month retention: memory cell suffers CCI (random coupling     |

|     | ratio) from neighbouring cell in vertical direction only                 |

| 5.4 | Simulation of memory threshold-voltage distribution after 1K P/E Cy-     |

|     | cles and 1 month retention: memory cell suffers CCI (constant coupling   |

|     | ratio) from neighbouring cell in vertical direction only                 |

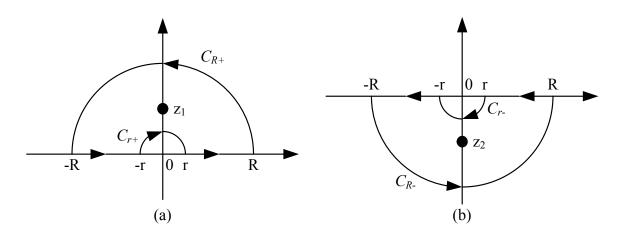

| 5.5 | Contours used for calculating the noise probability density function 115 |

| 5.6 | The effects of RTN, CCI, and retention noise on cell threshold voltage   |

|     | distribution after 1K P/E cycling and 1 year retention (from top to      |

|     | bottom: $L_0$ to $L_3$ )                                                 |

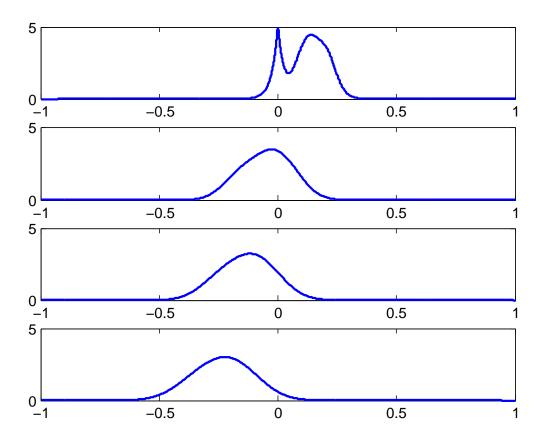

| 5.7 | Simulated curves to show the effects of RTN, CCI, and retention noise    |

|     | on memory cell threshold voltage distribution after 1K P/E cycling and   |

|     | 1 year retention                                                         |

| 5.8 | Cell threshold voltage distributions 4-level MLC flash memory 127        |

## List of tables

| 1.1 | NAND Characteristics                                             | 6  |

|-----|------------------------------------------------------------------|----|

| 3.1 | Comparisons of Resource Utilization in Tanakamaru's and Proposed |    |

|     | Designs                                                          | 60 |

| 4.1 | Simulations Setup                                                | 88 |

# Abbreviations

| ACG                                             | Asymptotic Coding Gain                                                                                                                                                            |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ALUT                                            | Adaptive Look-up Table                                                                                                                                                            |

| ALM                                             | Adaptive Logic Module                                                                                                                                                             |

| BER                                             | Bit Error Rate                                                                                                                                                                    |

| BM                                              | Branch Metric                                                                                                                                                                     |

| CCI                                             | Cell-to-cell Interference                                                                                                                                                         |

| ECC                                             | Error Correction Code                                                                                                                                                             |

| FTL                                             | Flash Translation Layer                                                                                                                                                           |

| FPGA                                            | Filed Programmable Gate Arrays                                                                                                                                                    |

| LLR                                             | Log-likelihood Ratio                                                                                                                                                              |

| HDD                                             | Hard Disk Drive                                                                                                                                                                   |

| ISPP                                            | Incremental Stair Pulse Programming                                                                                                                                               |

| 1511                                            | merementar Stan 1 uise i rogramming                                                                                                                                               |

| LDPC                                            | Low Density Parity Check                                                                                                                                                          |

|                                                 |                                                                                                                                                                                   |

| LDPC                                            | Low Density Parity Check                                                                                                                                                          |

| LDPC<br>MSED                                    | Low Density Parity Check<br>Minimum Squared Euclidean Distance                                                                                                                    |

| LDPC<br>MSED<br>MSB                             | Low Density Parity Check<br>Minimum Squared Euclidean Distance<br>Most Significant Bit                                                                                            |

| LDPC<br>MSED<br>MSB<br>MLC                      | Low Density Parity Check<br>Minimum Squared Euclidean Distance<br>Most Significant Bit<br>Multi-level Cell                                                                        |

| LDPC<br>MSED<br>MSB<br>MLC<br>ONFI              | Low Density Parity Check<br>Minimum Squared Euclidean Distance<br>Most Significant Bit<br>Multi-level Cell<br>Open NAND Flash Interface                                           |

| LDPC<br>MSED<br>MSB<br>MLC<br>ONFI<br>RTN       | Low Density Parity Check<br>Minimum Squared Euclidean Distance<br>Most Significant Bit<br>Multi-level Cell<br>Open NAND Flash Interface<br>Random Telegraph Noise                 |

| LDPC<br>MSED<br>MSB<br>MLC<br>ONFI<br>RTN<br>SM | Low Density Parity Check<br>Minimum Squared Euclidean Distance<br>Most Significant Bit<br>Multi-level Cell<br>Open NAND Flash Interface<br>Random Telegraph Noise<br>State Metric |

## Notations

| $V_p$                       | ISPP Verify Voltage                                              |

|-----------------------------|------------------------------------------------------------------|

| $\Delta V_{pp}$             | Program Step Voltage                                             |

| $V_e$                       | Threshold Voltage of Erased Cells                                |

| $V_i^{(k)}$                 | Threshold Voltage of the kth Programmed Level After Ideal Pro-   |

|                             | gramming                                                         |

| $\gamma^{(l)}$              | Coupling Ratio                                                   |

| $C_{bl}$                    | Bit Line Capacitance                                             |

| $\Delta V_{RTN}$            | Threshold Voltage Shift Caused by RTN                            |

| $\Delta V_{CCI}$            | Threshold Voltage Shift Caused by CCI                            |

| $\Delta V_{ret}$            | Threshold Voltage Shift Caused by Retention Noise                |

| I <sub>pre</sub>            | Average Current Consumption in the Pre-charge Phase              |

| n <sub>bl</sub>             | Number of Bit-lines Charged in Parallel                          |

| $N_{TH}$                    | Threshold Value for the Stripe Pattern Elimination Algorithm     |

| $d_{min}$                   | Minimum Euclidean Distance                                       |

| $(X_l \rightarrow X_{l+1})$ | State Transition from $X_l$ to $X_{l+1}$                         |

| $E_s$                       | Average Power                                                    |

| $\lambda(X_k, X_{k+1})$     | Branch Metric                                                    |

| V <sub>max</sub>            | Threshold Voltage for the Highest Programming Level              |

| $\widetilde{p}(x)$          | Overall Distribution of Total Noises Induced Threshold Voltage   |

|                             | Shifts                                                           |

| $\widetilde{p}^{(k)}(x)$    | Probability Density Functions of Noise-induced Threshold Voltage |

|                             | Shifts                                                           |

| $L(b_i)$                    | LLR of the <i>i</i> th Bit Stored in One Memory Cell             |

## Chapter 1

## Introduction

Hard disk drives (HDDs) have been around for a half century as the primary type of external storage drive in the computing industry. An HDD uses magnetism to store data on a rotating platter. A read/write head floats above the spinning platter reading and writing data. A faster spin rate for the platter generally means faster HDD performance. Typical laptop drives today spin at either 5400 RPM (revolutions per minute) or 7200 RPM, though some server-based platters spin at up to 15,000 RPM. The major advantage of an HDD is that it is capable of storing lots of data cheaply. Currently, 1 terabyte (TB) of storage is not unusual for a laptop hard drive, and the density continues to increase. However, HDDs are becoming less attractive today because of its long read/write access latency, high energy consumption and fragility. Due to the physical limitations of the mechanical devices, the time used to locate the data on the spinning disk can be as much as a few milliseconds, resulting in a relatively long access latency (e.g., compared to solid state memories). The mechanical elements also induce high power consumption and risk of failure. Having several moving parts means the hard drive is prone to damage and read or write errors if it is moved too vigorously or too frequently without sufficient protection.

The disadvantages of HDDs are not a critical limitation for computer systems because there are alternative technologies for external storage. For instance, solid state drives (SSDs) offer a range of sizes and capacities to meet a range of computing needs. SDDs are attractive for overcoming the above limitations of HDDs. SSDs are data storage devices using integrated circuit assemblies as memory to store data persistently. It is generally built over non-volatile semiconductor memories, such as NAND flash memories. Compared to HDDs, SSDs are more durable as they feature a non-mechanical design of NAND flash mounted on circuit boards. They are commonly shock resistant up to 1500g/0.5ms. SSDs have a second advantage with respect to data access. SSDs can have 100 times greater performance, almost instantaneous data access, quicker boot ups, faster file transfers, and an overall snappier computing experience than HDDs. Regarding power consumption, SSDs use significantly less power at peak load than hard drives, less than 2W versus 6W for an HDD. Their energy efficiency can lead to longer battery life in notebooks, less power strain on system, and a cooler computing environment.

Regarding the storage media of SSDs, the NAND flash memory represents a large proportion and has gradually become dominant due to increasing capacity and decreasing per-bit cost. These factors help to relieve the concerns of many people that SSDs are substantially more costly than traditional drives per byte. Such advantages come from several fundamental revolutions in the semiconductor technologies. Firstly, the flash density has been driven year over year through aggressive silicon feature size scaling (shrinking the size of a transistor). Today the NAND flash technology has reached 1Xnm, where "1Xnm" denotes that the design rule of the NAND flash memory is in the range of 10 to 20 nm, from the 250 nm generation technology one decade ago. Moreover, the trend for NAND flash memory is anticipated to continue in the near future, and the storage density will continuously be increased.

The second technology revolution is the use of compact architectures in designing the NAND flash memories, in which an array of memory cells share a common word-line where all memory cells or a part of them are programmed or read simultaneously. On the other hand, up to 32 or 64 memory cells in series are connected to share a bit-line and an on-chip page buffer that hold the data being programmed or fetched. Using this architecture, the NAND flash memories achieve highly efficient storage, and the silicon areas can be greatly saved. Thirdly, multi-level cell (MLC) NAND flash, which uses multiple levels per cell to allow more bits to be stored within the same number of transistors, is being used in designs to increase the flash storage capacity. For MLC NAND flash, the storage efficiency increases linearly with the number of bits programmed to each cell. Compared with single level cell (SLC) NAND flash, the 3-bit per cell flash memory, also known as the triple-level cell (TLC), and 4-bit per cell NAND flash can increase the storage capacity by nearly 3 and 4 times, respectively. Aside from the low cost and high capacity, the NAND flash memory is also attractive for SSDs because it adopts some excellent technologies to improve the data programming speed, for example, the Double Data Rate (DDR) NAND, and multiple logical unit numbers (LUN) operation.

It has been predicted that the worldwide data traffic will increase to 26.2 million TBs in 2015, which means data centres should upgrade their capacity to deliver up to 15 times their current capacity. Considering the benefits provided by NAND flash based SSDs, and the increasingly data traffic, it is expected that the SSDs will eventually replace HDDs in most of the applications in the near future.

### 1.1 Motivation

Despite its attractive features mentioned above, the challenges for using NAND flash memory are considerable as well. One of the shortcomings that has attracted the attention of researchers for years is the data reliability problem [19]. In the simplest terms, the data stored in NAND flash is represented by electrical charges that are stored in each cell, which approaches a certain programming level of the MLC NAND. When reading data from the memory, the voltage in the memory cell are sensed and compared to the programming levels to decide the original bits. Due to the noise and interference occurring in the NAND flash memory, the bits read from each cell are not usually consistent with the original information programmed but are affected by an output error probability.

By studying the new technologies used in flash memories, researchers first discovered that the memory scaling degrades the reliability as it introduces larger bit-line capacitance causing more interference during programming, more specifically, cell-to-cell interference. Cell-to-cell interference rises quickly as the bit-line capacitance increases, and has been well recognized as the major noise source in NAND flash memory. Secondly, the MLC technology increases more errors than SLC and reduces the reliability as well. Apparently, adding more bits to each cell makes it more difficult to distinguish between levels, lowering both reliability and performance. The reading circuits have to detect the threshold voltage of the memory cell and determine the information residing in it. Indeed, determining whether a container is either full or empty (SLC) is much simpler than determining whether it is one quarter full, one half full, three-quarters full, or entirely full (MLC).

Another side effect of storing more bits per cell is an increase in the rate at which the NAND cells semiconductor degrades. The level of a NAND cell is determined by the number of electrons present on the floating gate. The oxide layers that trap electrons on the floating gate wear out with every program and erase operation. This means the reliability reduces and more errors occur as the increase of program-erase (P/E) cycles. When the memory cells wear out, electrons become trapped, which affects the overall electrical properties of the cell and consequently subsequent program and erase operations. With the oxide weakened, charges sometimes leak from the floating gate, making the detection of programming level even difficult in the reading circuit. Although this is not a huge problem with SLC NAND because there are only two levels to distinguish between, it can be a huge problem for a TLC NAND because there are eight levels to distinguish and very little room for differentiation --- just a few electrons can make the difference between one state or another. The raw bit error rate (RBER) can be measured as an useful reliability metric for storage systems [45]. It has been experimentally shown that the RBER for 70xnm MLC can be as high as  $10^{-2}$  under the condition that the P/E cycling number is greater than 200,000. The condition could be even worse in the enterprise applications where flash is generally written at a much higher rate than in the client space.

All the NAND flash data errors caused by the physical factors mentioned above can be grouped into two classes: program disturb and data retention errors. The first class errors happen in the programming process while the second one in the data retention process. These errors have caused serious data reliability problems for storage systems based on NAND flash. If not dealing with them properly, there will be a large amount of incorrect data discovered after retrieving the information from the storage systems.

One way to reduce the errors is the use of write pattern processing technology. In view of the overall situation, the data pattern are random before being programmed to the memory array. The key idea of write pattern processing is to change the randomness of the data and intentionally distribute the data to some levels of MLC flash that have higher reliability. The technology mainly aims to reduce the errors occurring in the data retention process where the four levels of MLC flash have different reliabilities. Some researchers have been trying to apply this idea to the NAND flash memory controller to explore its capability in improving the reliability. The experimental results have shown that NAND reliability can be improved, and data retention errors can be reduced with data pattern processing. However, the scheme also brings a cost to the flash controller implementation because it consumes considerable hardware resources and increases complexity. Since the flash controller has a heavy load already in current practice because of several required components, such as the bad blocks management, it is very important to design a write pattern processing algorithm that is implementationoriented and consumes as little hardware resources as possible. On the other hand, the programming of data sequences will result in increase of current, and in this regard, it has been shown that the energy consumption differs significantly depending on the types of the sequences. As the written pattern processing will modify the data sequence, it is also desirable for the algorithm to reduce the power consumption of flash programming. In designing the pattern processing algorithm, this energy problem should also be considered as well as the hardware complexity.

Another efficient way to mitigate both program disturb and data retention errors is the use of error correction codes (ECC). NAND relies heavily on robust ECC to compensate

|                     | SLC     | MLC    | TLC    |

|---------------------|---------|--------|--------|

| Bits per Cell       | one     | two    | three  |

| Cost per Capability | highest | medium | lowest |

| Performance         | best    | medium | worst  |

| Reliability         | best    | medium | worst  |

| ECC Complexity      | highest | medium | lowest |

Table 1.1 NAND Characteristics

for its inherent weaknesses and has become an indispensable part of NAND flash memory systems. In the era of SLC, the simple Hamming code is used frequently although it can correct a limited number of errors only. For MLCs equipped in most NAND applications today, the Reed-Solomon (RS) codes and Bose-Chaudhuri-Hocquenghem (BCH) codes are being used to achieve better performance. All these ECCs are based on hard decisions making their error correction capability limited in general. Due to continuous advances in technology scaling and the fact that more bits will be added to each memory cell, data reliability will get even worse in the future solid state memories. Therefore, more advanced error correction codes based on soft decisions, such as turbo codes or low density parity check (LDPC) codes will be the popular ECC algorithms used for future NAND flash systems. The advanced error correction schemes can usually provide higher error correction ability but result in higher software or hardware design complexity. Table 1.1 illustrates the ECC requirements of NAND flash in different densities.

Among several soft-decision ECC algorithms, the LDPC codes are very promising because of their capacity-approaching ability in the additive white Gaussian noise (AWGN) channel. Additionally, the codes can be implemented with parallel decoding schemes to achieve high throughput. All these excellent features have made the LDPC-NAND a hot topic in the area of flash coding, and researchers are interested in removing any obstacles that may prohibit the application of LDPC coding. Generally speaking, there are three main challenges to adopting LDPC codes in SSDs, which includes designing LDPC codes of good performance, exploring approaches to address the LDPC decoder input initialization problem, and minimizing read latency induced by LDPC decoding [77]. Firstly, the construction of LDPC codes is quite tricky since different

structures for the same size LDPC may lead to very different performance. The good candidates for error correction of NAND flash memory should achieve a low error floor and fast convergence speed. Meanwhile, for additional improvement in error-correcting performance, it would be a plus for the codes to contain the redundant parity checks. Those prerequisites make the construction of LDPC codes for NAND flash channel more complicated than the similar case for digital communication channels.

Secondly, the NAND flash memories provide hard decisions only due to the intrinsic characteristics of the sensing circuits that decide the original bits during reading process. While the LDPC decoder requires to be initialized with soft inputs, more efficient ways have to be developed to get the required initialization values [30]. This has actually become a critical issue recently for the LDPC-NAND error correction applications. On the one hand, the flash channel is not easy to be precisely modelled. Simple Gaussian models are usually adopted for flash coding research but the channel noise distribution is actually far different from the Gaussian function. On the other hand, non-uniform quantization can usually achieve more fine-grained soft-decisions than traditional uniform quantization, however, it is difficult to find a good quantization scheme in the unknown flash channel.

The third challenge is the read latency caused by the LDPC decoder circuitry [76]. To obtain the soft decisions for LDPC codes, multiple-precision sensing should be used but it results in significant data access latency overhead. The read latency dramatically limits the throughput of storage systems and becomes critical today as the data speed of storage interfaces is getting faster and faster. For example, the Universal Serial Bus (USB) 3.0, a commonly used interface for storage systems today, is over ten times faster than the USB 2.0 used in the past.

This work is motivated by the problems discussed above. We wish to investigate NAND flash channel, the flash error correction coding, and the flash memory controller from the physical perspective. We propose and investigate efficient solutions to those problems. The next section describes the goals of this thesis in detail.

#### **1.2 Goals**

All throughout this thesis, the main intention is to improve the data reliability of NAND flash memories. To this end, based on the discussions above, we shall focus the research work on two topics: the data pattern processing and error correction. The problems related to the topics will be investigated from the intrinsics of NAND flash memories, and we aim to propose solutions based on the behaviours of the memory channel. Hardware complexity will be considered as well since both the processing unit and ECC module are implemented in flash controller in practice. The research goals set up for the doctoral projects are listed below.

- 1. The first goal is to explore the physical connections between data patterns and the flash read bit errors. The error probabilities based on different data patterns shall be quantitatively analysed through either software or hardware simulation. Based on discovered results, it is expected to propose a hardware-oriented write pattern processing algorithm to improve the data reliability of MLC flash memories. Ideally, the proposed algorithm shall exhibit better performance and lower complexity over the existing work in this direction. It is also preferable that the proposed algorithm is designed without facing too many implementation issues in the current practice.

- 2. In addition to the write pattern processing, this thesis also targets error correction in flash memories. With respect to ECCs, the second research goal is set in the dissertation to discover ways of extracting the soft information from the hard decisions output of MLC flash memory. The performance of the classic multiple reads method shall be evaluated by simulating a number of different reads over MLC flash memories, and the disadvantages can be pointed out quantitatively. Based on the experimental results, and the application background of LDPC coding, it is expected to propose an error correction scheme that issues a novel soft extraction algorithm and employs LDPC codes. The presented scheme shall exhibit better error correction performance than the existing flash LDPC coding

mechanisms. In the meantime, it is also expected that the soft extraction methods shall be easy to implement and not induce much overhead in the sensing circuits.

- 3. This thesis aims to find an efficient way to quantize the sensing outputs for the memory reads. Both the uniform and non-uniform sensing quantization schemes will be investigated and simulated using the flash memory access model. The read latency and complexity for different quantizations are compared, and the critical factor influencing the performance shall be figured out. In the end, it is expected to discover an optimized sensing quantization scheme that results in lower read latency and can be applied in flash memory with the proposed ECC scheme to achieve good performance.

- 4. The final goal is to characterize the flash memory channel and build a channel model that fits the real situation as much as possible. Various existing channel models are based on different kinds of approximation, while this thesis is trying to propose a model without using too much approximation. All channel sources of noise, distortion and interference shall be taken into account when calculating the channel distribution, and it is expected to present accurate probability density functions for the channel noise and final threshold voltage of each programming level. Based on the results, future research may find out better solutions for the future research in flash coding.

### **1.3** Thesis Contribution

Several approaches have been used in this work to meet the research goals. The first way is to investigate the storage systems and digital communication systems and compare both from the intrinsic view. Keeping the differences in mind, some techniques used in communication systems can be applied to flash memory and achieve remarkable performance, provided only that the techniques be modified properly to fit in the application. To mathematically characterise the channel distribution, another important approach using the characteristic function of random variables is used in this thesis. Based on the approaches and experimental results, this dissertation creates a channel model for NAND flash memory and develops efficient fault tolerant solutions to improve the reliability of flash-based data storage. The main contributions of this thesis are summarized as follows.

- 1. This dissertation studied the practical low-complexity schemes that deal with data pattern processing. A write pattern formatting algorithm (WPFA) is presented to eliminate column stripe patterns and reduce the proportion of flash cells on high threshold-voltage levels. The WPFA improves data reliability and relieves the power pressure of flash memory effectively. With the proposed scheme, SSD systems consume low energy and avoid suffering huge current spike. Compared to the current design practice that employs asymmetric coding and stripe elimination algorithm (SPEA), the proposed algorithm consumes less overhead of NAND cell area and exhibits better performance on power consumption. Associated hardware design issues are considered with the aim of reducing complexity and utilizing less logic resources. The advantages of the proposed scheme have been evaluated by various metrics using both computer simulations and FPGA implementation. Due to all these benefits, the proposed algorithm will be an attractive solution for practical low-complexity data pattern processing schemes of SSDs.

- 2. As for the flash controller, the ECC module comes after the data pattern processing scheme. Following the WPFA algorithm, this dissertation designed a novel fault tolerant solution for flash memory that concatenates trellis coded modulation (TCM) with an outer LDPC code. The concatenated TCM-LDPC fulfilled the error correction capability of LDPC coding to achieve reliable storage in multilevel flash. Moreover, the error correction performance is further improved since TCM can decrease the raw error rate of MLC and hence relieve the burden of outer LDPC code. Compared to the flash coding system that provides hard-decisions and employs Bose-Chaudhuri-Hocquenghem (BCH) codes only, results show remarkable BER performance improvements from the system equipped with

LDPC codes and pragmatic TCM. This dissertation has also derived mathematical formulations to quantitatively analyse the asymmetric coding gain achieved in flash channels.

- 3. Another contribution that comes with the TCM-LDPC is the way it used to get the soft values. Thanks to the Bahl, Cocke, Jelinek, and Raviv (BCJR) algorithm, the TCM decoder can extract soft information from the hard-decision outputs of flash read circuits. Such approach will not influence the sensing circuits, and thus introduces less read latency than the classic multiple reads method. Given the soft initialization values, the decoding of LDPC codes is feasible; as a result, the BCJR and TCM will be a useful alternative in practice to extract flash memory soft information.