**City Research Online**

# City, University of London Institutional Repository

**Citation:** Zarrin, J., Aguiar, R. L. & Barraca, J. P. (2017). Manycore simulation for petascale system design: Motivation, tools, challenges and prospects. Simulation Modelling Practice and Theory, 72, pp. 168-201. doi: 10.1016/j.simpat.2016.12.014

This is the accepted version of the paper.

This version of the publication may differ from the final published version.

Permanent repository link: https://openaccess.city.ac.uk/id/eprint/18147/

Link to published version: https://doi.org/10.1016/j.simpat.2016.12.014

**Copyright:** City Research Online aims to make research outputs of City, University of London available to a wider audience. Copyright and Moral Rights remain with the author(s) and/or copyright holders. URLs from City Research Online may be freely distributed and linked to.

**Reuse:** Copies of full items can be used for personal research or study, educational, or not-for-profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

City Research Online:

http://openaccess.city.ac.uk/

publications@city.ac.uk

# Manycore Simulation for Peta-scale System Design: Motivation, Tools, Challenges and Prospects

Javad Zarrin<sup>a,\*</sup>, Rui L. Aguiar<sup>b</sup>, João Paulo Barraca<sup>b</sup>

<sup>a</sup>Instituto de Telecomunicações, Campus Universitário de Santiago, Aveiro, Portugal <sup>b</sup>Universidade de Aveiro, Aveiro, Portugal

# Abstract

The architecture design of peta-scale computing systems is complex and presents lots of difficulties to designs, as current tools lack support for relevant features of future scenarios. Novel systems must be designed with great care and tools, such as manycore architecture simulators, must be adapted accordingly. However, current simulation tools are very slow, often specific-purpose-oriented, suffer from various issues and are rarely able to simulate thousands of cores. The emergence of peta-scale systems and the upcoming manycore era brings nevertheless new challenges to computing systems and architectures, adding further difficulties and requirements on the development of the corresponding simulators. Furthermore, the design of architecture simulators for manycore systems involve methods and techniques from various interdisciplinary research areas, which in turn brings more challenges in different aspects. As system complexity grows, the growth of the simulation capacity is being outpaced (reaching the so called simulation wall). In this paper, we present the challenges for simulating future large scale manycore environments, and we investigate the adequacy of current modeling and simulation tools, methodologies and techniques. The aim of this work is to highlight how current approaches can best deal with the identified problems, smoothing the challenges of research in future peta-scale systems.

Keywords: architectural simulations, manycore simulators, full-system simulation, manycore systems, computer architecture

# 1. Introduction

Current trends in computation technology have focused in improving performance by increasing the number of cores per die (parallelism) rather than by increasing the rate of clock frequency of each core, due to the exhaustion of the Moore's law. Many companies and academic communities pushed this trend, designing multicore and manycore systems with capacity of tens to hundreds of cores per single die. These manycore processors are more like data-centers-on-a-chip than previous single processors, as a complex communication network connects the different cores. It is predictable in a near future to consider systems with a very large interconnect network in manycore machines with dimensions from thousands to millions of cores.

A consequence is that both system design and programming concepts must increasingly focus in heterogeneous parallelism. Future parallel and distributed applications, compilers, operating systems and tools must be able to scale well with the hardware nature of manycore and distributed execution. However, increasing the number of cores on a die increases the complexity of hardware designs, and has considerable impacts which result in enlargement of the potential design-space. Moreover, it brings serious challenges particularly for memory hierarchies and on-die interconnect bandwidth, both within the die and off die.

Systems must then be designed with great care and tools, such as manycore architecture simulators, must be adapted to address these disruptive challenges. Manycore simulators (i.e. manycore architecture simulators) can assist researchers from different areas. These areas include software (such as programming models, operating systems, compilers, etc.), hardware and computing architectures to model and assess future systems. The upcoming manycore era brings new challenges to computer architects that must be paralleled by the development of adequate architecture simulators. Ideally, to simulate a fully parallel system we can expect that an efficient architecture simulator should (at-least) be able to be parallelizable, and use the benefit of concurrency, enabling faster evaluation of future systems. Moreover, architecture simulators should provide a highly scalable, fast and accurate model to describe, emulate/simulate and measure the hardware details, memory hierarchy and interconnection networks. Furthermore, they must meet the stringent requirements along the lines of productivity, multi-modeling, synchronization, modularity, and event sampling capabilities. However, these properties are not true for the majority of the currently available architecture simulators. As complexity grows, the performance of a single simulated CPU core slows down, and the usage of these sequential simulators (i.e. architecture simulators) will be mainly limited by the performance of simulating a single CPU.

Note that, in this paper, we use the term "simulator" to refer to "architecture simulator" or "manycore architecture simulator" which differs from its more general meaning. We use the term "manycore simulation tools" in a slightly more general way to cover a wider range of contexts (methods and techniques). In

<sup>\*</sup>Corresponding author. Tel:+351 234 377 900, Fax: +351 234 377 901 *Email addresses:* javad@av.it.pt (Javad Zarrin), ruilaa@ua.pt (Rui L. Aguiar), jpbarraca@ua.pt (João Paulo Barraca)

other words, a simulator (architecture simulator) is a type of manycore simulation tool. Furthermore, the term "emulator" (or architecture emulator), as used in this paper, also differs from its general meaning in other research fields. In this paper, an emulator means a simulator which lacks support for performance measurements. In fact, we associate an emulator with functional correctness only. This means that the notion of time for an emulator is imprecise and often just a representation of the wallclock time of the host. We use the term "emulation" to refer both to "functional simulation" and to describe the act of an emulator.

The rest of this paper is organized as follows. In Section II, we discuss why manycore architectural simulation is needed, particularly for research on peta-scale systems. Section III presents in detail our taxonomy to addresses current modeling and simulation tools, as well as the methodologies that could be exploited and enhanced in order to design next generation efficient simulators. In Section IV, we provide an overview of recently proposed simulation tools for architectural analysis, which are able to simulate the entire execution cycle of application for the target systems. Other simulator types, such as those that mainly focus on physical modeling aspects (e.g. power, energy and thermal) or interconnect simulators (e.g. Network on Chip simulators), are out of the scope of paper for conciseness. In Section V, we extract and elaborate a set of major problems and challenging issues created by manycore simulation. Finally, in Section VI, we present our conclusions, followed by a discussion of future directions for research. This includes possible approaches and solutions which can be used to solve the problems and deal with the challenges identified.

#### 2. Simulation and Peta-scale Systems

Peta-scale systems are defined as systems which are able to provide peta-FLOPS, millions of billions of FLoating OPerations per Second, computational power [1, 2]. They can be described as the increasingly massive and dynamic networks of interconnected diverse processors and components (i.e. elements). Such as system, as a whole, exhibits a set of properties and behaviors among the elements, which are not distinguishable from the properties of the individual processors and components. These systems are only on its infancy currently, but in future peta-scale manycore systems, we can expect to have computing nodes with more than 10 thousands cores per node. We can also expect to have much more diversity (heterogeneity) of cores, interconnections and architecture designs compared to today systems.

Architectural simulation is a common method for studying and analyzing different architectures, designs and algorithms for various target systems through imitating the operation of real-world processes, processors and systems over time. Architectural simulation acts as a low cost alternative to experimentation on real systems by representation of key characteristics, behaviors and functions of the real systems. The objective of simulation is to provide capability to researchers and designers to flexibly and efficiently explore a design space. This can include analyzing the performance of current systems (e.g. architecture assessment), acquiring and predicting processor/system behaviors and evaluating novel designs. Simulation enables today's designers to analyze and predict different aspects (such as performance, reliability and efficiency) of future's machines. This means that simulation is a particularly useful tool when the desired target systems, such as peta-scale systems, do not currently exist in reality. However, current simulation tools are very slow, often specific-purpose-oriented, suffer from various issues and are rarely able to simulate more than 2000 cores (we discuss current simulation tools further in Section 4). Furthermore, introducing the concept of peta-scale system presents more requirements that must be fulfilled by current simulation tools. We discuss these requirements and their corresponding issues further in Section 5.

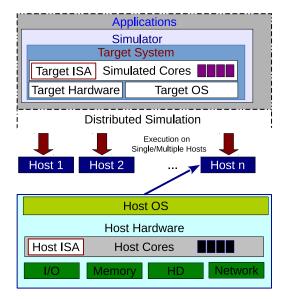

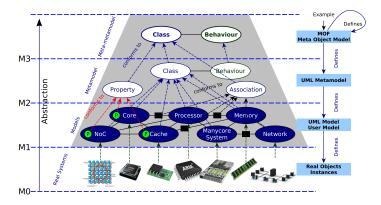

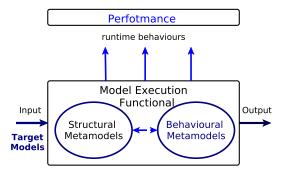

Figure 1 demonstrates a generic structure for (software-based) simulation. As it is shown in the figure, a simulator is an application software which runs on single host or multiple networked host machines (distributed simulation). The target system is the system which needs to be simulated by simulator. Depending on user requirements the target system might be a partial system or a full system including target (simulated) OS. The term "target Instruction Set Architecture (or target ISA)", as used in this paper, refers to the ISA of the processor architecture simulated. Similarly, the term "host ISA" refers to the ISA of the host machine which runs the simulation. Note that, it might be possible to have some similarities between a target system and its host system (e.g. target ISA = host ISA or target OS = host OS). In such a case, a simulator can alternatively employ a different simulation approach which might be faster (or easier to implement) (see Section 3). More details of this structure are discussed in the next section.

Figure 1: Overall Simulation Structure

## 3. Manycore Simulation

Simulators are essential tools for the design and evaluation of computer and system architectures. Taking in consideration the

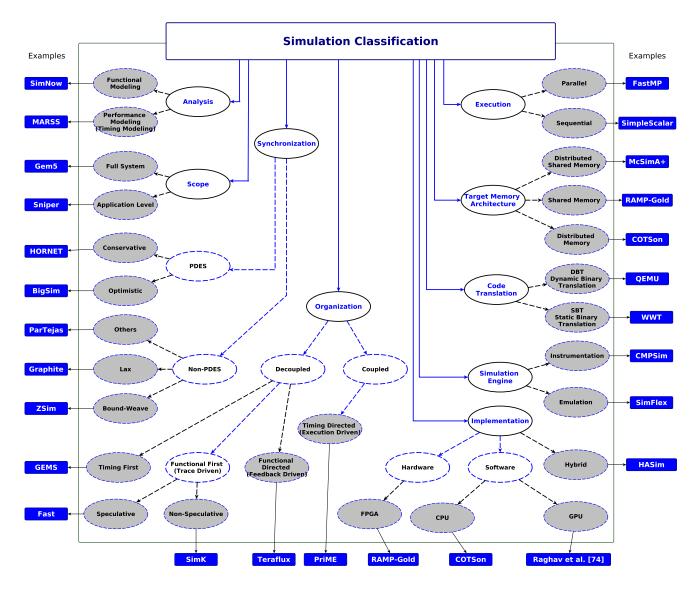

Figure 2: Simulation Classifications

objective of the evaluation, there are a large variety of different simulation tools, techniques and methods in the current literature. Figure 2 presents a snapshot of the most important classifications for manycore simulation tools and related technologies. Figure 2 also presents example simulator for each category (note that a simulator can be in multiple categories). We discuss these classifications and their related concepts in detail in Section 3.1.

#### 3.1. Terminology and Classifications

There are plentiful tools, methods and techniques for manycore simulation in the current literature. These can be classified along many dimensions, such as: user/application-level vs fullsystem; functional vs timing; trace-driven vs execution-driven; cycle-driven vs event-driven. In the following, we discuss and briefly explain the terminology and concepts associated with some of the most important classifications.

**Emulators vs Simulators:** Emulators are tools able to demonstrate the functional behavior of the system, focused on

the exact reproduction for an external system. They repeat the function of a target platform on a host platform. Simulators differ from the former because they consider an abstract, simplified model and do not try to replicate all the aspects of a system. A simulator in addition to ensuring the functional correctness, must provide capability to study and analyze the performance of proposed system/hardware designs by using accurate timing information.

**Functional vs Timing/Performance:** According to our terminology (see Section 1), architecture emulators include only functional models while simulators contain both functional and performance models. The functional model (functional partition) is in charge for the correct execution of the target Instruction Set Architecture (ISA) (i.e. architectural modeling). In addition, functional models may provide facility to observe the interactions among processors, memory and I/O peripherals without modeling micro-architectural details. As examples of the tasks for a functional model we can mention aspects as decoding instructions, updating simulator memory and verifying the floating point operations.

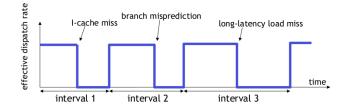

The performance model (timing partition) is responsible to drive a functional model. This is done by providing accurate timing information in a way that simulating a particular microarchitecture (at least in a specific aspect) would be possible (i.e. micro-architectural modeling). In other words, a timing model is able to determine the time the target architecture takes to execute an instruction. Examples of the tasks for the timing model include making decisions to select the next instruction for execution, tracking branch mispredictions, and predicting the clock cycles to execute instructions.

Creating a new functional model might be complex in terms of implementation, optimization and verification, but after that, it can modularly be coupled and reused across various timing models. On the other hand, implementation of only a timing model with capability to reuse an existing functional model can be much easier and less time consuming than developing a complete simulator (including both functional and timing models) from scratch. Unlike functional models, the correctness of target architectures (in term of ISA functional) is not of primary concern for timing models. What matters is to track and control the accuracy of micro-architecture-specific timing details [3].

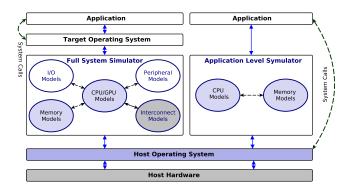

**Simulation Scope:** An architectural simulator is defined as a piece of software which mimics the behavior of a real computer system with ability to estimate performance and outputs for a given input (application). It may model different computer devices and components (i.e. only a single target microprocessor, or an entire computer system including processors, memory system, and I/O devices) with different level of details. The simulation scope specifies the scope of target systems that an architectural simulator can model. According to this, we classify the processor simulators (i.e. architectural simulators) into two categories: full-system simulators and user/application level simulators (see Figure 3).

Figure 3: Full System Simulator vs Application Level Simulator

A full system simulator provides capability to run a detailed, complete and real software stack on the target (simulated) system without any modification. The software stack might be OS, complex applications such as multithreaded and multiprocess workloads, or applications that highly exercise system calls, I/O and networking. The full system model generally includes processor cores, memories, network and interconnection, buses, peripheral devices and privileged modes. However, the supported models and the level of details for each model are various for different simulators. A full system simulator, besides timing/performance modeling might also supports simulation of the physical models such as power, energy and thermal. Gem5 [4], Flexus (SimFlex) [5], and MARSS [6] are some examples of full system simulators.

Furthermore, full system simulators can be very important design tools, particularly for System-on-Chip (SoC) simulation where it is necessary to efficiently cope with the huge hard-ware/software design space. SoC architecture integrates all components of a (electronic/computing) system (including complex hardware/software) into a single integrated concept. This provides capability to scale computing performance / power efficiency through combining (massively parallel and high performance) manycore processors, Network-on-Chip (including several network/interconnect communication protocols) and software (including OS and various computing intensive user applications) [7, 8].

On the other hand, user/application level simulators model only the user side of applications without OS support. They rely on the host machine (host OS) to service the system calls and execute a given user code of a benchmark on top of the simulator. These simulators are easier to develop and use, since they do not boot an OS. But they are also limited to only support specific workloads. In other words, they can not run applications such as multithreaded and JVM workloads that frequently use applications that are sensitive to system time like and client-server workloads. As examples of user/application level simulators we can mention SimpleScalar [9], BigSim [10], Graphite [11], Sniper [12], ZSim [13] and PriME [14].

Simulator Organization: Each simulator generally contains functional and timing partitions which interact in order to form a complete simulation. According to whether the functional and the timing partitions are completely separated or not, simulators can be categorized into decoupled and coupled. Coupled simulators potentially can provide flexibility for developing precise simulations (i.e. highly detailed simulation), due to speculative execution modeling (producing all the values and possible side effects) and timing-dependent outcomes. However, this flexibility is reduced when there is need for frequent modifications of functional or performance models. In other words, complexity arises due to new complex devices (functional models), modern performance/timing models and their internal interactions. For coupled simulators, it is challenging to address multiple different conflicting demands (such as simulation precision, accuracy, flexibility and performance) in a single simulator component which integrates both functionality and timing modeling. On the other hand, decoupled simulators aim to reduce this complexity by completely decoupling functional and timing models. Accordingly, they can achieve better flexibility and potentially other advantages such as accuracy (through correctness verification) and modularity (which can lead to faster development and easy modification) [15]. The drawback for this approach is to introduce redundancy which may reduce the simulation performance. Moreover, decoupled simulators typically call an external simulator/emulator to perform functional modeling. This might increase the difficulty for modeling interactions among functional and timing models.

Based on the type of interaction or the relationship between the functional model and the timing model, the simulators can use different organizations. A taxonomy of microarchitectural simulator organizations is introduced in [15] and [16]. We extend those taxonomies and classify the simulator organizations into the following five categories (Table 1 presents the advantages and disadvantages for each of the aforementioned simulator organizations):

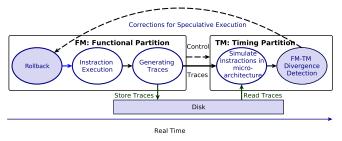

1- Functional First (Trace Driven): The functional-first is a completely decoupled approach. The functional model is separately executed first, and later, when the functional modeling is finished, the timing model is run. As demonstrated in Figure 4, the functional model executes instructions and produces traces that are streams of information about the execution. Traces are then fed into the timing partition where the microarchitectural simulation is performed. Depending on whether speculative execution is supported or not, the functional-first organization can be categorized into speculative and non-speculative.

Figure 4: Functional First Organization - The gray elements (rollback and mismatch detection) are only supported by speculative-functional-first organization

The speculative functional-first assumes that all parts of execution (not just for branch control) are speculative. When the timing partition detects that the execution in functional partition has differed from the timing partition, it asks the functional partition to undo or rollback the effects of wrong path for instruction execution, and to redirect fetch. Examples of this approach include UTFast [17], FastSim [18], SimpleScalar [9], Zesto [19], ReSim [20], BigSim [10] and Transformer [21].

Unlike speculative approach, in non-speculative functionalfirst, rollback mechanism is not supported. This means that the timing partition independently provides the timing model in a highly decoupled fashion and regardless of any potential execution divergence (mismatching functional execution and timing model). Non-speculative approach might be easy for implementation and parallelism through a highly modular and decouple design. However, it potentially suffers from execution divergence issues which results in being inadequate for modeling timing-dependent execution behaviors (such as interactions among threads in a multithreaded application). Examples of this approach include single thread work load simulators (like PTCMP [22]).

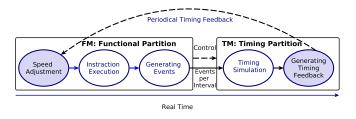

2- Functional Directed (Feedback Driven or Event Driven): The functional-directed is a completely decoupled approach where the functional model drives the timing model. The functional model is assumed to be accurate, but timing feedback from the timing model is needed in order to correct the timing behavior. As we can see in Figure 5, using a timing feedback mechanism, the timing model periodically adjusts the speed of functional execution to reflect the timing estimates. This gives the running application a more-precise timing correction. COTSon [23] and Teraflux [24] use this approach.

Figure 5: Functional Directed Organization

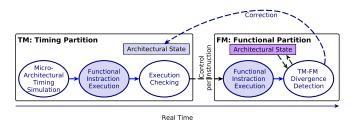

3- Timing First (Instruction Driven): The timing-first is a decoupled approach which uses the timing model to drive the functional model. Figure 6 demonstrates the timing-functional interactions for this organization. The timing model runs ahead of the functional model and simulates the functional behavior (i.e. instruction execution) in addition to the timing simulation.

Figure 6: Timing First Organization

But the functional execution (for each instruction) must be checked and verified later by the functional model. This means that the functional model is only used for checking; when a mismatch (execution divergence) is detected, the timing model is notified by the functional model for the correction. In such a case, the architectural state of the timing model is reloaded from the functional partition. Examples of timing-first organization include TFsim [15], FeS2 [25] and GEMS [26].

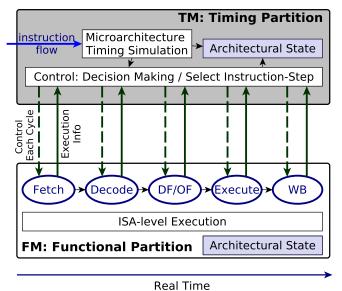

4- Timing Directed (Execution Driven or Cycle Driven): In timing-directed simulators, functional and timing models are tightly coupled. As we can see in Figure 7, multiple interactions (per instruction) between timing and functional model raise system complexity. The timing model processes the flow of instructions through micro-architectural timing simulation. In each cycle, it directs the functional model with which step (e.g. fetch, decode, operand fetch, memory access, execute, writeback) of which instruction should be executed. Accordingly, the functional model returns the execution information to the timing model for each step. In timing-directed organization, the architectural state in both (timing and functional) partitions are naturally matched with each other, thereby preventing execution divergence. Talisman [27], Graphite [11], ZSim [13] and PriME [14] use this organization.

Table 1: Advantages and disadvantages of various simulator organizations

| Simulator Organization             | Pros                                                                                                                                                                                                                                                                                 | Cons                                                                                                                                                                                                                                    |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Functional-First (Non-Speculative) | Easy implementation and parallelization, Highly-<br>decoupled design, On-way data flow, Highly-Modular,<br>Support for binary translation, direct execution and<br>compiled-code simulation                                                                                          | No support for speculative execution, Not able to model<br>timing-dependent outcomes between threads, No correc-<br>tions for the timing model, Mismatching functional exe-<br>cution and timing simulation (i.e. execution divergence) |

| Functional-First (Speculative)     | Matching between functional execution and timing simu-<br>lator, Support for speculative execution and multithreaded<br>applications, Natural parallelism of the functional and<br>timing simulator, On-way data flow                                                                | The functional model must support speculation, The tim-<br>ing simulator needs to implement some of the functionality<br>behaviors                                                                                                      |

| Functional-Directed                | Efficient trade-off between high speed functional modeling<br>and high accurate timing simulation, Highly-adapted with<br>sampling techniques, Support speculative execution and<br>multithreading                                                                                   | Periodical feedback has impact on the simulation accuracy.                                                                                                                                                                              |

| Timing-First                       | Single timing-functional call per instruction, Fast devel-<br>opment, Debuggability of the timing simulator, Matching<br>between functional execution and timing simulator.                                                                                                          | No support for accurate modeling of interactions between<br>threads, The timing simulator needs to implement almost<br>all functionality behaviors.                                                                                     |

| Timing-Directed                    | Highly-accurate, Natural support for speculative execution<br>and multithreading in timing partition, Potential support<br>for memory and memory consistency modeling, Easy val-<br>idation of the timing simulator, Matching between func-<br>tional execution and timing simulator | Highly-coupled design, Complex functional modeling,<br>Highly frequent inter-partition (timing-functional) com-<br>munication which impacts the simulation speed, Multiple<br>functional-timing calls per instruction.                  |

Near Time

Figure 7: Timing Directed Organization

Simulator Execution: The execution of simulations on the host machines can be either sequential or parallel. Sequential simulators are highly accurate but as the complexity of the target architecture increases the simulation speed significantly decreases [28, 29]. There are numerous examples of sequential emulators and simulators in the literature including QEMU [30], Embra [31], Mambo [32], SimNow [33], SimpleScalar [9], Simics [34], SimOS [35], Rsim [36], Gem5 [4] and PROTEUS [37]. While most of these tools are able to model multicore architectures and multi-processors (in parallel chips), they are all limited to only utilizing a single processor on a single host machine which leads to significant slowdown in simulation speed. Parallel emulators (e.g. PQEMU [38], COREMU [39], Paral-

lel Mambo [40], and Parallel Embra [41]) and simulators (e.g. FastMP [42], SlackSim [43], Wisconsin Wind Tunnel Simulators (WWT) [44, 45], CMPSim [46], ZSim [13], MARSS [6], SimFlex [47], GEMS [26], COTSon [23], Graphite [11], Sniper [12, 48] and BigSim [10]) enhance the performance of simulation (in terms of simulation speed) by dividing and distributing the simulation workload across multiple cores on multiple host machines. However, parallelizing a simulator without sacrificing simulation accuracy is challenging. Furthermore, the execution of functional and timing models might be different. For example, COTSon [23] uses SimNow [33], a sequential emulator, for functional modeling, while it benefits of a parallel timing model.

**Parallelization and Synchronization Strategies:** Synchronization overhead is one of the major challenges for parallel simulation [49]. Different parallelization strategies and synchronization algorithms such as Parallel Discrete Event Simulation (PDES) [50], Lax synchronization [11] and Bound-Weave parallelization [13] have been proposed for parallel architectural simulators. Along this line we can classify parallel simulators based on their parallelization techniques into PDES-based and non-PDES-based simulators.

**I. PDES-based Synchronization:** PDES aims to facilitate fast execution of large simulation programs. It refers to the parallelization strategies for distributed simulation through execution of a single discrete event simulation program on a parallel computer [50]. Many of the conventional parallel micro-architectural simulators in the literature such as HORNET (conservative) [51], BigSim (Optimistic) [10], SimK (conservative) [52], SlackSim (hybrid) [43] and COTSon [23] are based on PDES. Using PDES, the components of the simulator are divided across host threads. The time-stamped simulation events from each component are distributed among multicores in parallel chips of multiple host machines. These events are executed concurrently while maintaining the causality relationship (i.e. cause and effect relationship) between them. This means that some sequencing order

between events executing in two separate processes must be maintained, although maintaining this causality relationship is challenging while exploiting inherent parallelism for faster job scheduling [53].

PDES-based synchronizations can be broadly classified as conservative (pessimistic), optimistic and hybrid. Conservative approaches, using pessimistic estimates, only process events when it is safe to do so. The events are scheduled in time stamp order while avoiding deadlocks efficiently. The synchronization is performed every time an ordering violation (causality error) may happen. On the other hand, in optimistic approaches, all events are executed speculatively and once an ordering violation is detected, the recovery can be performed by invoking a rollback mechanism.

There are several classic algorithms for conservative and optimistic synchronizations including asynchronous-conservative [54], Lower Bound Time Stamp (LBTS) [55] and optimistic time warp [56]. In asynchronous-conservative, there is no need to perform any global synchronization. Instead, various deadlock avoidance algorithms can be applied to ensure that only safe events in the future queue are processed. Using LBTS, in each cycle, the events in the future queue which have the lower bounded time stamp are executed while time progressing is managed by a global reduction and synchronization mechanism. In optimistic time warp, a causality error is detected whenever the time stamp of the received event message by a process is smaller than the process's clock. Many other PDES based synchronization mechanisms have been proposed in the last decade such as conservative null message (or CMB) [57], conservative forecast null message (FNM) [58].

PDES-based parallel simulators might support single or multiple synchronization algorithms. For example, Manifold [59] supports multiple standard PDES algorithms including LBTS [55], CMB [57], FNM [58] and time quantum synchronization [59].

Parallel simulators based on Optimistic-PDES generally suffer from poor scalability due to frequent roll-back and synchronization. On the other hand, simulators based on conservative-PDES provide better scalability due to their simplicity and less synchronization overhead in comparison with optimistic based simulators [51, 60]. Nevertheless, both approaches provide reasonable accuracy [13]. The scalabity for parallel simulators means that the simulation speedup constantly rises when the number of allocated host processors for simulation is increased [61]. Over the decades of research in the field, many optimization methods such as Lazy Cancellation [62], Lazy Reevaluation [63], Direct Cancellation [50], Early Cancellation [64], Space-time Simulation, Optimistic Time Windows [65], Wolf Calls [66] and Time Warp Straggler Message Identification [67] have been proposed to improve the overall performance of PDES based Simulators. However, PDES based parallel simulators are not yet truly competitive with performant sequential simulators with respect to simulation accuracy and scalability.

**II. Non-PDES-based Synchronization:** Non-PDES based parallel simulators such as Sniper [12, 48] and Graphite [11], relax synchronization requirements to obtain scalability by permitting micro-architectural events to occur out of order. How-

ever, these approaches provide complexity to model the actual behavior of the target system components such as memory controllers and shared caches while they sacrifice the simulation accuracy. In fact, Graphite leverages lax synchronization models to enable trade-offs between simulation speed and simulation accuracy while Sniper (which is built on Graphite) uses higher levels models by reducing accuracy compromise. ParTejas [68], a more recent work, is a shared memory based parallel simulator written in Java. Unlike Sniper and Graphite, ParTejas doesn't rely on highly relaxed synchronization, but rather it primarily relies on novel concurrent data structures. In fact, it uses a lock free parallel slot scheduler for synchronizing the accesses of multiple threads at a shared resource while uses flexible barriers known as phasers to relax synchronization within bounds. ZSim [13] is one of the latest parallel simulators that provides an alternative approach for synchronization which is called Bound-Weave. ZSim simulation runs in time quanta where each time quanta is defined as a small interval (e.g. 1000 cycles). ZSim divides each time quanta (interval) into two parallel phases: bound phase and weave phase. In the bound phase, similar to the lax synchronization, the cores are simulated without simulation of the interactions among the cores (i.e. unordered simulation), but the core-memory access traces for all the cores are recorded. In the weave phase, parallel event-driven simulation is performed by using the traces to simulate the memory accesses in order. Bound-weave is proposed based on the assumption that pathaltering interference is extremely rare. This is a right assumption but only for cores that implicitly communicate through the cache hierarchy. Thus, bound-weave parallelization methods are not applicable to other communication styles (e.g. extremely fine-grained message-passing across whole chip). Moreover, simulating speculation (e.g. transactional memory) and complex workloads (e.g. kernel-intensive applications) would be difficult since ZSim is a user-level simulator. ZSim also provides limitations to model multi-threaded cores, detailed NoC models and virtual memory (TLBs).

In summary, we can claim that non-PDES-based simulators provide better scalability than PDES-based simulators, but they suffer from inaccuracy of simulation.

**Simulation Engine:** The simulation engine specifies the underlying strategy which each simulator uses to perform functional modeling. As we already discussed at the beginning of this section, the main responsibility of the functional model is the correct execution of the simulated ISA (i.e. emulation). But the ISA emulation might not be necessary when simulators directly use the host's ISA, instead, simulators can use instrumentation. This indeed eliminates the need for functional model for such simulators and increases the simulation speed with the potential cost of limiting the ISA of the target machines to only the host's ISA.

Depending on which strategy is used for the simulation engine, we classify the simulators into emulation-based (or interpretation-based) and instrumentation-based. An emulationbased simulator either uses its internal emulator or leverages an external simulator/emulator to model functional behavior. The simulator interprets the instruction and according to the simulator's organization, invokes both functional and timing model

to execute the instruction for the simulated ISA. Emulation becomes the primary and even the optimal option, particularly when the simulated ISAs are supposed to be different from the host's ISA, or when the simulators are expected to be portable. On the other hand, instrumentation, is faster than emulation, since the instructions are directly executed on the host machine. The simulator adds instrumentation calls to the simulated binary in order to interact with the timing model by calling the timing model before each basic block or memory operation. Instrumentation provides facilities to understand the execution behavior of each instruction and measuring the execution performance on the host machine. It returns a set of useful information about the execution which can fed the timing model. This can be done by enabling transparent access to the state of host's processor and memory after each instruction execution. Furthermore, instrumentation can be very efficient, particularly when emulation and functional modeling become difficult for complex ISAs. Most of the current instrumentation-based simulators run on x86 hosts, since x86 is common in both desktop and server segments, and the ISA's impact is less relevant. Examples using emulation strategies include MARSS [6], Gem5 [4], SimFlex, COTSon and BigSim while simulators such as CMPSim [46], Graphite [11], PriME [14], ZSim [13] and McSimA+ [69] benefit from instrumentation strategies.

**Binary (Code) Translation:** Binary translation is the core technology for both emulation and instrumentation strategies through enabling translation techniques to translate binary codes from a simulated architecture to the host architecture. The main difference is that, in emulation, all the functional and execution behavior of the applications for the simulated architecture are modeled through a functional model. In instrumentation, they use instrumentation calls added to the translated binary. Thus, arbitrary statistics about the run-time actions of the executing application can be gathered from the host which can be used to specify the functional behavior of the application for the target architecture without needing a complete functional model.

Two main types of binary translation techniques are static (ahead-of-time translation) and dynamic (translation at run time).

In Static Binary Translation (STB), all the binary code of an executable file is converted into code that can be executed on the host architecture, and after that the translated code is run on the host. This might not be efficient, since discovering some part of the code may depend on the run-time values (e.g. indirect branches, dynamically loaded libraries and self-modifying code). Wisconsin Wind Tunnel (WWT) [70] is a simulator which uses static binary translation.

On the other hand, Dynamic Binary Translation (DBT), relies on on-line code translation which means that that the portions of the binary code (each short sequence of code or single basic block), are translated and executed one after another in the order; the code is only translated as it is discovered. DBT suffers from large amount of overhead during translation which leads to increased execution times. Code cache is a technique which reduces the translation overhead by caching the translated code sequences for later usage when subsequent executions of the same code region can use the already translated code.

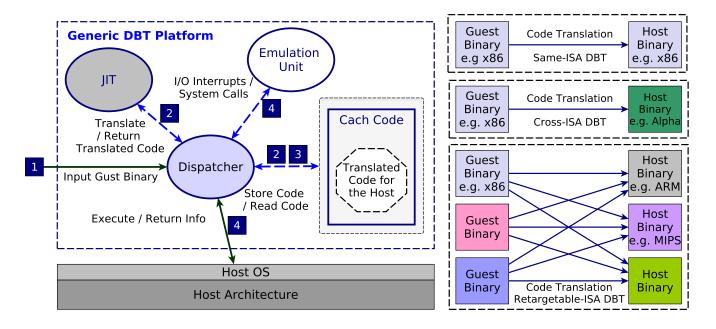

Figure 8 presents the general framework of the DBT systems

which includes four main components: dispatcher, just-in-time compiler (JIT), emulation unit and software-based code cache. The dispatcher coordinates translation and execution of the code through directing other components. It gets the address of the next program which is a segment of guest binary code and determines whether a translated copy of that code is available in the code cache. If so, the execution is resumed in the code cache, otherwise, the dispatcher kick-starts the JIT compiler to translate the untranslated guest code segment. JIT fetches the code segment, and then optimizes and translates the code to the host binary in the software code cache. Optimization can be performed by adding, removing, inserting or replacing instructions to the code before translation. Using this capability, JIT allows to inject various instrumentation instructions into code. Furthermore, the JIT's granularity to fetch and translate (i.e. amount of code which are proceed at a time) can be specified as a basic block, a trace, a treegion, or an entire procedure. The emulation unit is also responsible to handle exceptions and interrupts (such as I/O interrupts for full-system simulation and system calls for user/application level simulation) during execution.

DBTs enable virtualization across ISAs by emulating a guest binary executable code in one ISA on a host machine with a same or different ISA. Modern DBTs also employ dynamic recompilation techniques (e.g. just-in-time compilation). This way, the translated code is instrumented to return information about the execution of each portion of the code which in turn can be used to optimize the rest of the execution (e.g. incremental optimization of hot regions). DBT has been widely used for many different purposes and applications (such as performance optimization, debugging, profiling, performance motoring and application migration). DBT, depending on the simulated ISAs and the host's ISA, can be classified as simulation engine into three categories: same-ISA, cross-ISA and retargetable (see Figure 8). For the same-ISA, the simulated ISA is identical to the host's ISA. In cross-ISA, guest ISA differs from the host ISA. In retargetable DBT, the guest ISA (simulated ISA) can be retargeted for multiple different ISAs. Both same-ISA and cross-ISA can be considered as dedicated DBTs, since the guest and host architecture are fixed. Dedicated DBTs are limited by assuming that the register set of the host architecture is the same or richer than the guest architecture. This causes lack of translation flexibility and adaptation to highly heterogeneous environments.

Many of the current instrumentation-based simulators such as Graphite [11], PriME [14] and ZSim [13] benefit from DBT tools and libraries which leverage same-ISA DBT on x86 host architecture. Examples of these DBT systems include Pin [71], StarDBT [72], and DynamoRIO [73]. Emulation-based simulator generally leverage cross-ISA and retargetable DBTs to perform virtualization and emulation. IA-32 [74] and FX!32 [75] are examples of cross-ISA DBT systems. There are few DBTs in the state of the art which have been designed for retargetability. Among them, QEMU [30] is a well-known emulator which implements retargetability. It enables binary translation from several different guest ISAs such as x86, PowerPC, ARM and SPARC on multiple common host architectures such as as

Figure 8: General DBT Framework and DBT Types

ARM, SPARC, Alpha, x86, MIPS and PowerPC. Retargetable DBTs broadly suffers from large emulation overhead ahead of translation, since the guest architecture must be fully virtualized by software in the memory, prior to translation. They also suffer from optimization overhead as well as code optimization overhead. Furthermore, providing near native and high quality translated code is another challenging issue for retargetable DBTs.

**Target Memory Architectures:** Depending on the memory architecture of the target simulated systems, manycore simulators can be categorized into shared memory, distributed memory and distributed shared memory.

In shared memory architecture, all the simulated processors simultaneously have access to a common single memory space in order to avoid data redundancy and facilitating inter-processor communications. In this way, the processors do not need to know where data resides, but they might suffer from race conditions. In distributed memory architecture, each simulated processor has its own private memory. Whenever communication is required (e.g. requesting a remote data), the simulated processors can communicate with each other through simulating message passing techniques on top of the simulated network and interconnect. Thus, it is necessary for every distributed memory simulator, to provide capability for network modeling (such as on-chip network). For example, RAMP-Gold [76] is a shared memory simulator which doesn't provide any network model. But distributed memory simulators such as COTSon [23] and BigSim [10] support network modeling.

Distributed memory simulators are more flexible than shared memory simulators for parallel simulation, since every simulated processor (i.e. a core) can independently be run on a different processor of a different host in the system. In distributed shared memory architecture, each node of a cluster has access to a shared memory in addition to its non-shared, private memory. Distributed shared memory simulators (e.g. SimK [52] and Mc-SimA+ [69]) are generally required to support complex models of memory subsystems (i.e. memory and cache hierarchies) as well as communication networks.

**Implementation:** Depending on the strategy to implement functional and timing models, simulators can be classified into software-assisted simulators (i.e. simulators based on software simulation of the target architectures on CPU/GPU hosts), hardware-assisted simulators (i.e. simulators based on implementation of the target architectures on FPGA hosts) and hybrid simulators (i.e. simulators based on combination of both software and hardware simulation).

Most of the current architectural simulators are softwareassisted, since software simulation is low cost, easy to develop, and flexible to explore various target architecture. COTSon, GEMS, SystemC [77], SimFlex and BigSim use software based simulation on CPU for both functional and performance models. In [78], authors introduce a software based simulator which runs on both CPU (by leveraging QEMU for functional modeling) and GPU (by proposing a GPU-based manycore accelerator). The work presented in [79] is another recent example of software based simulators. It leverages QEMU for software based functional modeling on CPU while uses a performance model, written in C and CUDA, designed to execute partly on the host CPU and partly on the host GPU.

On the contrary, hardware-assisted simulators are high cost and not flexible for architectural design exploration. They also take significant amount of time, memory and effort to develop and use, but they provide faster simulation speed compared to software-assisted simulators. Examples include RAMP Gold [76], that uses FPGAs for both functional and timing models. ProtoFlex [80] and FAST [18] are examples of hybrid simulators, where they use FPGAs to accelerate the performance model while using software based simulation for functional models. Furthermore, hybrid simulators like HASim [81] use FPGAs for functional modeling and CPU based software simulation for performance modeling.

**Sampling:** Sampling and reduction techniques enable faster simulation of large scale execution workloads through simulating representative portions of execution (i.e. samples) [82]. In this way, architectural simulators can be classified based on their sampling strategies. There are various methods for execution sampling in the current literature. Examples include random sampling [10], dynamic sampling [23] and statistical sampling [47, 83] such as SimPoint [82] and Sampling Micro-ARchiTecture Simulation (SMARTS) [83]. Sampling techniques might reduce the simulation accuracy and precision in the estimate.

Assuming that a population is a complete set of elements (e.g. execution instructions of a complete workload) which need to be simulated. Sampling means simulation of a sample workload, instead of a complete workload. Each sample includes a subset of population (i.e. a set of sampling units) where a sampling unit is defined as a quantum of population. An ideal sampling approach must create a sample with choosing a minimal but (highly) representative set of sampling units in order to provide a reliable and quantifiable simulation (in terms of accuracy and speed).

A random sampling is performed by selecting and simulating only a random sample from the entire workload (the whole population) through a random selection of a fixed number of sampling units. The number of selected sampling units (or the sample size) must be sufficiently large for obtaining reliable (in terms of accuracy and precision in the estimate) simulation results (close to complete workload simulation). In a systematic (or periodical) sampling, sampling units are chosen from a population at periodical intervals. A uniform sampling, perform this with equal selection probability for (all) sampling units distributed in the entire population. In a representative sampling, sampling units are chosen from weighed regions of the population. In a dynamic sampling, the sample intervals (and the duration of each interval) are determined dynamically through monitoring the variation of execution behavior for the given benchmark [84].

Statistical sampling attempts to estimate (simulate) the execution behavior and characteristics of a given workload (i.e. a population) by selecting and simulating an optimal sample. This can be done by examining the adequacy of potential samples over the entire population using priori profiling (preprocessing), consisting statistical analysis (for example in terms of total, mean, and proportion) of the code. In other words, an statistical sampling prescribes a specified and constructive mechanism to determine an optimal sample (including a large number of tiny sampling units) in order to obtain a desired confidence interval. The sample must be able to capture the inherent variations of the given stream of execution instructions [85]. Statistical sampling is an efficient approach in capturing average behavior. And also it can specially provide an appropriate sampling when the population benefits from a clear internal control and contains a large number of similar transactions. However, it might be more complex and time consuming compared to non-statistical sampling approaches [86, 87].

#### 3.2. Virtual Machines

Systems based on Virtual Machine (VMs) hypervisors are typical tools to model the hardware. These provide an emulated environment where the guest applications (particularly operating systems) can be executed virtually, very close to the way that they are executed on real hardware. Generally, virtual machines are faster than architecture emulators. This happens because the hypervisors create environments where substantial amount of instructions execute directly on the real underlying hardware without any overhead. VMs also permit execution times near to native speed. However, without support for hardware virtualisation, performance may be severely degraded, and not all currently available processors support virtualisation. They should meet a set of requirements which are elaborated in [88]. Of course, these can only be used when the system to test already exists, precluding the usage of VMs for many design space exploration tasks.

#### 3.3. Architecture Emulators

Architecture emulators are software tools which emulate the behavior and characteristics of a given CPU. They do not directly run the instructions of the emulated processor on the underlying real host processor. Rather, they employ methods of interpretation, or of dynamic translation, to translate the emulated instructions to a corresponding set of instructions for the target platform. Then, they execute the translated instructions on the hardware of the host platform. Therefore, architecture emulators generally decrease execution speed, but dynamic translation, a cache intensive technique, is used to enhance the speed.

Definitely architecture emulators are appropriate tools to be embedded in manycore full simulators for the purpose of functional modelling due to their accuracy, and reasonable speed. Qemu [30] and SimNow [33, 89] are common examples of architecture emulators which have been employed in several full-system simulators.

Qemu is an open source full system emulator which uses the dynamic translation technique. It provides capabilities to emulate several types of CPU architectures (x86, PowerPC, ARM and Sparc) on several different hosts (x86, PowerPC, ARM, Sparc, Alpha and MIPS) to virtually run a complete and unmodified operating system. It also offers three operation modes: full system emulation mode, where the processor architecture and other peripheral devices are emulated; user mode emulation, where Qemu can launch executables compiled for one processor on another host processor which could have a completely different architecture; and finally Qemu acceleration mode, which executes most of the code directly on the hardware without dynamic translation, resorting to different execution rings.

AMD SimNow is a fast cycle, accurate full system emulator, using caching and dynamic compilation techniques. It can support booting an real operating system and launch complex applications over it. The SimNow emulator supports the x86 and x86-64 instruction sets, with support for other devices of a real system. It performs emulation of the real system with (at least) 10x slowdown in comparison with the native execution. SimNow cores generate a series of event that are stored in the asynchronous queues. COTSon provides timing feedback for SimNow instances, it parses asynchronous queues to create higher level objects such as instructions. COTSon is a complete tool which provides timing information back to the functional emulator in order to affect the behavior of the application. It also uses quantum based simulation [23, 59] as synchronization technique. Quantum is the smallest, atomistic timing entity. i.e. the dimension of length ("time") as a single entity is a quantum. In this way, every time a quantum starts, the timing module will get a notification about the staring time and the quantum length. Similarly once a node ends a quantum, the timing module will let the other modules to know about the network timing information which has been calculated during the past quantum. The functional simulation adds extra latency to all packets submitted, because network packets are sent twice. The source Network Interface Card (NIC) sends packets to the mediator timing module and the mediator will send the packets to the target NIC module. Additional time is required to for the packet processing in the mediator, therefore COTSon uses a Quanta (Q) bigger than real latency time between two nodes [90].

#### 3.4. Network on Chip, Thermal and Energy Aspects

Most full-system simulators can simulate the interconnection network (particularly the Network On Chip (NoC)) as well as the entire processor and memory system. However, due to inherent limitations, they are not able to perform NoC simulations, in a very detailed level [91]. ASIM [92] is an example of this case. It is a full-system simulator, used in industrial laboratories, that simulates the processing cores and memory hierarchy. It only models ring interconnects and it cannot model other interconnects such as mesh, hypercube, x-tree, shuffle exchange, fully connected, butterfly, cube connected cycles, etc. RSIM [93] and SESC [94] are other examples of full-system simulators, whose interconnection network is not modeled precisely in these frameworks. On the other hand some of the simulators support modeling of the entire system, including the on-chip network, to a significant degree of detail, such as PharmSim [95].

For the purpose of designing new manycore simulators and particularly with the objective of modeling the future peta-scale parallel machines, we should consider a very efficient and accurate network-on-chip model. NoC is an integral part of the memory system and not modeling its details leads to an unsatisfactory model. Today, there are several NoC only simulators like NOXIM [96] and SICOSYS [93] which are used by the NoC community for experiments. However, these are not able to be used to perform full-system modeling and simulation.

In the current literature, SystemC [77] (refer to Section 4.3), a simulation framework, has been widely used to design full system simulators and particularly for NoC simulators. SystemCbased NoC simulators [97–103] are powerful tools to evaluate different NoC configurations by means of simulation. Xpipes [103] is an example of this type. It provides capability to simulate both homogeneous/heterogeneous NoC architectures for multiprocessor SoCs through using a set of flexible SystemCbased NoC macros, enabling to act as instance-specific network components at instantiation time.

One of the efficient solutions to enhance the capability of a full-system simulator is leveraging other accurate and highperformance network on chip simulators for NoC modeling instead of using a weak built-in network model. It is required for each of the simulator component and tools to provide modularity. SICOSYS [93] is an example which has been plugged into RSIM [36] for simulating symmetric multiprocessor systems.

Energy consumption in uniprocessor architectures grows linearly with the clock rate frequency and quadratically with voltage. Usually, lowering frequency permits operation at smaller voltages, and this has a cubic effect on energy savings. As for multicore and manycore processors, the power consumption increases linearly with the number of cores while clock frequency increases at a much slower pace [104]. Further, the use of identical processing elements in an homogeneous architecture reduces the overall hardware complexity and verification process in the entire development cycle.

Other than power consumption, thermal issues have a significant impact on the performance of manycore architectures. Simulating the thermal behavior of the manycore processors is an important objective in many different aspects. The architecture designers need to know and analyze the impact of their designs on the temperature of the processors. Similarly, thermal modeling is required by the OS and system designers. The problem is that this kind of modeling is computationally expensive. In processors, thermal time changes in time interval of the order of ten milliseconds. Thus, to simulate a very complex thermal impact of a proposed design, it is required to simulate the system in a high level of details at least for several seconds.

In manycore architectures, thermal status of the individual cores are related to the actual computing workloads of each core. Thus, analytical [105] and mathematical models as Fourier expansion [106] can be used to characterize and model manycore processor workloads and foresee the accurate amount of the processors load.

In the current literature, various tools and simulators have been proposed to investigate power consumption and energy efficiency of microprocessors and manycore architectural designs. Examples include Wattch [107], SimplePower [108], SoftWatt [109], XTREM [110], Orion [111], Orion2 [112], McPAT [113], Sim-PowerCMP [114], PrEsto [115], Sniper/McPAT [116], Manifold [59] and [117], providing capability for power or thermal modeling of computing processors. However, since physical modeling (power, energy and thermal) of manycore systems is out of the scope of our interest in this paper, we do not discuss the details of those approaches here.

#### 4. Architecture Simulators

Parallel and distributed simulation tools such as SimFlex [47], GEMS [26, 118], FastMP [42], SlackSim [43, 60], BigSim [10] and COTSon framework [23, 89], have been created in order to enhance the performance of simulation by concurrently distributing the simulator workloads among several parallel hosts.

Furthermore, running parallel manycore simulators in accelerated hardware platforms such as FPGAs, and more recently in general purpose GPUs, helps to increase the throughput of the system simulation.

Architectural simulators provide capability to simulate either the target microprocessors, or the full hardware and software functionality of the target machines, as platforms, where platforms may consist of parallel processors, memory hierarchy, storage devices, I/O devices, compiler, OS, etc. Along the line of the growing issues in manycore era architectures, simulators have changed and they used new approaches to solve the problems and improve the system efficiency. They started from a simple approximate uniprocessor simulator, and continually improved to the recent high efficient clustered simulators.

Table 2 provides a generic comparison of architecture simulators and other simulation tools. However, this comparison is very general and depending on each specific tools it might differ. The table shows that simulators (both types) are the more flexible tools to analyze and predict the behavior of future systems. Furthermore, emulation-based simulators are the most powerful tools, since they can potentially simulate any type of architectures. On the other hand, instrumentation-based simulators are faster, since they provide near-native execution speeds.

In the remaining of this section, we discuss some of the most important architecture simulators that have been proposed in the last decade.

# 4.1. SimpleScalar

SimpleScalar [9] is one of the oldest uniprocessor serialized software simulators, which previously was widely used by the research community focused in processing architectures. As well as other similar simulators, SimpleScalar was limited to only run single-threaded, user-mode workloads. With the advances in manycore micro-architectures, researchers and designers are more interested to use simulators with the capability to run multithreaded workloads, and to model large number of processing cores along with the memory subsystem and interconnects.

#### 4.2. BigSim

BigSim is a parallel simulator and performance modeling system which is particularly designed to study parallel programming issues [10]. It can predict performance of parallel applications on machines (like IBM Blue-Gene/L systems) [119] with a very large number of processors (i.e. large number of processing nodes). This is done by actual execution of real applications on smaller machines (i.e. small number of processing nodes). Indeed, BigSim can be used for the architecture design of manycore-enabled HPC systems. It has been built on POSE [120] and includes several components. POSE is a generalpurpose optimistically synchronized PDES (parallel discrete event simulation) framework which is designed for scalability of fine-grained parallel and distributed large-scale discrete event simulations. However, its load-balancing framework still needs to be improved. BigSim simulates the behaviors of communication and computation separately in two steps. At first, it uses an emulator to execute an application, containing number of virtual

processes, on a small number of physical processors to generate trace logs. At the next step, a trace-based simulator uses the log files and simulates activities on a much larger processing system.

BigSim directly executes the application (in small scale) using its emulator and mimics the behavior of the target platform (in large scale). The direct execution creates significant demands on host CPU and memory. For this reason, the simulator allows skipping computations and instead simulates latencies that would be resulted by executing those computations. But the problem is, this works only for data-independent applications, due to the fact that some part of the data are not really computed. The simulator explores the inherent determinacy of several parallel applications. But still it is not an application-independent performance modeling system and its functionality is limited to specific applications. Moreover, tracing in BigSim is specifically designed for its implementation language Charm++, and doesn't support the message passing applications.

BigNetSim, a BigSim's component, uses a simple analytical model (e.g. SimGrid [121]) to simulate interconnection networks by supporting detailed network models of various topologies. However it still doesn't provide capability for packet-level interconnections simulations (e.g. MPI-NetSim [122]) which is the most precise approach (while it is very resource-consuming) for network simulation. This leads to reduction in the overall system accuracy. In fact, the major drawback of BigSim is that it suffers from inaccuracy (with respect to the expected behaviors of the real system) caused by log-based postmortem simulation of the generated traces.

# 4.3. SystemC

The SystemC language [77] is an extension of C++, providing a cycle-accurate, event-driven, simulation interface for system-level modeling by describing modules of a target architecture as a set of C++ classes. It is a popular framework for SoC architecture simulation, providing a powerful interface to describe HW/SW components as well as interconnections between modules (ports and signals), facilitating description of interconnection between multiple SoC processors. SystemC also provides support for integrating different Instruction Set Simulators (ISS) in a unified system simulation framework, as it is able to plug an independent ISS into the entire simulation framework (as a new system module), where all system modules can be activated and synchronized through a common reference clock. Furthermore, SystemC based simulators (such as [123–127]) can benefit from advantages of C++ language as a hardware description language while bridging the gap between hardware and software description languages [123]. In fact, one of the most important advantages of C/C++ based description languages such as SystemC (or SpecC [128], a similar alternative) is their capability to concurrently specify both hardware and software components in the design (i.e. co-simulation of both hardware and software). This is a necessary requirements for full system simulators (system level).

In the current literature, SystemC has also been extensively used for designing NoC simulators, due to the powerful capa-

Table 2: General Specifications of Simulators, Emulators and Virtual Machines (Execution Info: Information about the execution behaviour, Functional Results: Execution Results)

| Tools                            | Engine                     | Code Translation         | Output Information                 |

|----------------------------------|----------------------------|--------------------------|------------------------------------|

| Virtual Machines                 | Mainly Direct Execution    | Same-ISA DBT             | Functional Results                 |

| Emulators                        | Emulation (Interpretation) | Cross-ISA & Retargetable | Functional Results                 |

| Emulation-based Simulators       | Emulation (Interpretation) | Cross-ISA & Retargetable | Functional Results, Execution Info |

| Instrumentation-based Simulators | Instrumentation            | Same-ISA DBT             | Functional Results, Execution Info |

bility of SystemC to describe various interconnections between hardware components. Examples of this include [97–103].

SystemC based simulators are accurate and sufficient for validating hardware specifications. However, they might fail to adequately support embedded software (in terms of writing or debugging), which is an important requirement for SoC design [129], are often slow compared to the traditional ISSs like SimpleScalar.

MPARM [123, 124] is an example of such simulators. It is a full-system SystemC-based architecture simulator, enabling to model functional, performance, and power consumption aspects, as well as a complete OS for a Multi-Processor System-on-a-Chip (MP-SoC), in a cycle accurate manner. Using SystemC, MPARM (or MP-ARM) can provide processor models, memory models, the AMBA bus architecture (for communication between models through ports and signals) and support for parallel programming. However, the MPARM simulator is slow and its models for processing cores are very abstract and relatively simple, lacking detailed core modeling [130].

One of the conventional solutions to overcome the speed limitation of SystemC-based simulators is to integrate SystemC with QEMU, making possible to simultaneously benefit from accuracy of SystemC and speed of QEMU. However, interfacing between SystemC and QEMU might be challenging, since their combination must be capable of accessing all the hardware modeled in QEMU and SystemC for co-simulation of HW/SW. For doing this, SystemC needs the QEMU support to provide I/O operations (initiated by the processor), memory access interface, interrupt handling and also peripherals to access memory directly [131]. Furthermore, there are timing aspects which need to be taken into account for synchronization between SystemC and QEMU models [132], making SystemC-QEMU combination a complex task. There are several research works in the current state of the art, which perform this using different approaches [131, 133–136]. Among these types of simulators, Virtualsoc [8, 137] is a recent work for many-core-based accelerators, allowing the execution of a full-fledged Linux operating system.

# 4.4. Graphite

Graphite [11] was created for the exploration of large-scale manycore environments, as well as for research of isolated applications. It can be used as a distributed, high-level parallel simulator. In order to deliver the high performance and scalability needed for useful evaluations, it uses various methods such as direct execution, multi-machine distribution and analytical modeling. In addition, it benefits from lax synchronization schemes like LaxP2P [138–140] (a distributed synchronization technique, in which the progress of one core is periodically checked against another randomly selected core). Graphite has other important capabilities, such as its flexible and extensible architecture, its compatibility with commodity multicores and clusters, its ability to run off-the-shelf p-threads application binaries, and its support for a single shared simulated address space despite running across several physical host machines.

Graphite, unlike BigSim, FastMP and COTSon, allows the analysis of a much wider category of architectures. While it offers the possibility to model distributed memory architectures, it also provides a coherent shared memory between the simulator threads [11]. In addition, Graphite also models compute cores and interconnected networks while operates transparently through providing a single shared address space to off-the-shelf applications.

Graphite can simulate manycore target architectures with hundreds of cores launched on several parallel hosts, but the problem is that the simulator accuracy resides in the application-level. It is not very successful to deal with speed/accuracy challenges. Graphite has three different methods for synchronization: base model (or Lax synchronization), barrier (LaxBarrier or Lax with quanta-based barrier synchronization) [140] and random-pairs (LaxP2P or Lax with point-to-point synchronization). Lax lets the clocks differ and offers the highest performance and scalability. However, in order to keep the simulated clocks in reasonable agreement, Graphite needs to deploy application events to make them synchronized, otherwise it must let the threads run freely.

LaxBarrier and LaxP2P [58, 140] are the mechanisms on top of Lax to improve its accuracy. LaxBarrier is the most accurate synchronization methods of Graphite where all active threads must wait on a barrier after a configurable number of cycles. It has a relatively poor performance and scalability compared to the other two synchronization models. LaxP2P aims to achieve the accuracy of quanta-based LaxBarrier without reducing the scalability and performance of lax synchronization. Using this scheme each tile periodically chooses another random tile and synchronizes with it. If the clocks in the source and target tiles differ by more than the number of configured cycles then the tile which is ahead goes to sleep for a short period of time. LaxP2P is fully distributed therefore it creates less overhead than LaxBarrier. In comparison to the barrier method it provides more scalability and less accuracy [11].

# 4.5. SimK

SimK [52] is a framework based on the Parallel Discrete-Event Simulator (PDES) synchronization protocol [141] to develop system simulators. PDES [53] is a well known parallel distributed synchronization technique for parallel simulation. SimK provides simulation modules that target system components, such as CPUs and memory modules. All modules communicate through message passing methods, which enables them to run concurrently. A dedicated module maintains the time synchronization of all simulation modules. P-GAS [142], HPP-NetSim [143] and G-Cluster [144] are the simulators which have been developed based on the SimK framework.

Since each component has to synchronize the execution state with its peers, continuously at a microsecond rate, SimK employs several optimization strategies and techniques to avoid the severe performance degradation that synchronization would impose. Each node is handled by a single process, which further creates one thread per processor. A user level scheduling scheme is employed where simulation modules are dispatched to each thread. CPU affinity is used to avoid cache related performance penalties. Since the simulation modules run on the same process and share the same memory, SimK employs an asynchronous zero-copy [52] communication mechanism. Further synchronization optimizations are employed at the scheduling level to avoid blocking of the simulation modules. Other optimizations employed include lock-free queues, buffer management and load balance.

SimK requires a host shared-memory multiprocessor system. While it has shown to scale within this system, the lack of cache coherence on manycore systems does not allow the sharedmemory dependent approach used by SimK to be effective. Thus, the major bottleneck of this simulation framework, which is synchronization, cannot be solved with the approach taken by SimK on a manycore system. This severely limits the scalability of SimK to multiprocessor systems.

# 4.6. GEMS

GEMS [26, 118] is a full-system simulation platform capable of capturing detailed aspects of processing cores, cache hierarchy, cache coherence, and memory controllers. The simulation platform consists of a set of nodes connected with links allowing for wide variety of topologies, with each link having a particular latency and bandwidth. This has led to the widespread use of GEMS in the computer architecture research community, with a huge amount of contributions for validating research ideas.

A major limitation of GEMS is its simple interconnection model that serves as a communication fabric between various cache and memory controllers. Messages traverse the network hop by hop, which makes GEMS incapable of modeling a detailed router or a network interface. In fact it does not integrate a real interconnection network model [145]. Because of this limitation, GEMS ignores buffer contention, switch and Virtual Channel (VC) arbitration, realistic link contention and pipeline bubbles. The GEMS interconnect SimpleScalar model also assumes perfect hardware multicast support in routers. However, considering on-chip network designs, supporting fast and low power hardware multicast is currently still a challenge.