**City Research Online**

## City, University of London Institutional Repository

**Citation:** Anderson, P. (1990). Computer architecture for wafer scale integration. (Unpublished Doctoral thesis, City, University of London)

This is the accepted version of the paper.

This version of the publication may differ from the final published version.

Permanent repository link: https://openaccess.city.ac.uk/id/eprint/28487/

Link to published version:

**Copyright:** City Research Online aims to make research outputs of City, University of London available to a wider audience. Copyright and Moral Rights remain with the author(s) and/or copyright holders. URLs from City Research Online may be freely distributed and linked to.

**Reuse:** Copies of full items can be used for personal research or study, educational, or not-for-profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

# **Computer Architecture for Wafer Scale Integration**

Paul Anderson Department of Computer Science City University December 1990

This thesis is submitted as part of the requirements for a Ph.D. in Computer Science, in the Department of Computer Science of City University, London, England.

# Contents

| Acknowledgements                                             |           |  |  |  |  |  |

|--------------------------------------------------------------|-----------|--|--|--|--|--|

| Declaration                                                  |           |  |  |  |  |  |

| Abstract                                                     |           |  |  |  |  |  |

| · · · · · · · · · · · · · · · · · · ·                        |           |  |  |  |  |  |

| 0 Introduction                                               | 11        |  |  |  |  |  |

| 0.1 Wafer Scale Integration                                  |           |  |  |  |  |  |

| 0.2 Wafer Scale Communications                               |           |  |  |  |  |  |

| 0.3 Graph Reduction                                          |           |  |  |  |  |  |

| 0.4 Formal Specification of Hardware                         |           |  |  |  |  |  |

| 0.5 Contribution $\ldots$ $\ldots$ $\ldots$ $\ldots$         |           |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

| WSI and Parallel Architectures 17                            |           |  |  |  |  |  |

| <b>1 WSI and Parallel Architectures</b><br>1.1 Review of WSI |           |  |  |  |  |  |

| 1.1.1 Why WSI?                                               |           |  |  |  |  |  |

| -                                                            |           |  |  |  |  |  |

| 1.2 Parallel Architectures                                   |           |  |  |  |  |  |

|                                                              | tures     |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

| 1.3 Summary                                                  |           |  |  |  |  |  |

| Communications for WSI 29                                    |           |  |  |  |  |  |

| 2.1 Terminology, Metrics & Requireme                         | ents      |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

| 2.2 Review                                                   |           |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

| 2.3 The Navigation Algorithm                                 |           |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

| 8                                                            | algorithm |  |  |  |  |  |

| 2.4 The Paths Algorithm                                      | -         |  |  |  |  |  |

| •                                                            |           |  |  |  |  |  |

| 2.4.2 Properties                                             |           |  |  |  |  |  |

|                                                              |           |  |  |  |  |  |

|   |            | 2.5.1 Routing                                         |  |  |  |

|---|------------|-------------------------------------------------------|--|--|--|

|   |            | 2.5.2 Properties                                      |  |  |  |

|   | 2.6        | Summary                                               |  |  |  |

| 3 | A (        | A Graph Reduction Engine 65                           |  |  |  |

|   | 3.1        | Implementation Techniques for Functional Languages 66 |  |  |  |

|   |            | 3.1.1 Dataflow                                        |  |  |  |

|   |            | 3.1.2 Graph Reduction Architectures                   |  |  |  |

|   | 3.2        | Overview of COBWEB                                    |  |  |  |

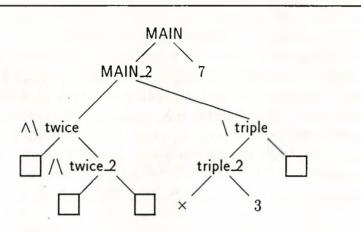

|   |            | 3.2.1 Hope <sup>+</sup> $\rightarrow$ FLIC            |  |  |  |

|   |            | 3.2.2 FLIC $\rightarrow$ COBWEB                       |  |  |  |

|   | 3.3        | Specification of COBWEB                               |  |  |  |

|   |            | 3.3.1 COBWEB as a Term Rewriting System               |  |  |  |

|   |            | 3.3.2 COBWEB in Paragon                               |  |  |  |

|   | <b>3.4</b> | Translating Paragon to hardware 89                    |  |  |  |

|   |            | 3.4.1 The Target Description                          |  |  |  |

|   |            | 3.4.2 The translation process                         |  |  |  |

|   |            | 3.4.3 A static synchronous system                     |  |  |  |

|   |            | 3.4.4 A static asynchronous system                    |  |  |  |

|   |            | 3.4.5 A Dynamic system                                |  |  |  |

|   |            | 3.4.6 The design of object processors                 |  |  |  |

|   |            | 3.4.7 A general purpose methodology                   |  |  |  |

|   | 3.5        | Design of COBWEB                                      |  |  |  |

|   |            | 3.5.1 Design of the COBWEB class topology             |  |  |  |

|   |            | 3.5.2 Methods for the Object Processors               |  |  |  |

|   | 3.6        | Results of Implementation                             |  |  |  |

|   | 3.7        | Summary                                               |  |  |  |

| 4 | AF         | Parallel WSI Cobweb 119                               |  |  |  |

| - | 4.1        | A performance model for WSI multiprocessors           |  |  |  |

|   | 4.2        | Specification of a multiprocessor Cobweb              |  |  |  |

|   |            | 4.2.1 The new classes                                 |  |  |  |

|   |            | 4.2.2 Packets                                         |  |  |  |

|   |            | 4.2.3 Agents                                          |  |  |  |

|   |            | 4.2.4 The Processor Class                             |  |  |  |

|   | 4.3        | Design and Simulation                                 |  |  |  |

|   |            | 4.3.1 The design                                      |  |  |  |

|   |            | 4.3.2 Assumptions                                     |  |  |  |

|   |            | 4.3.3 Code distribution                               |  |  |  |

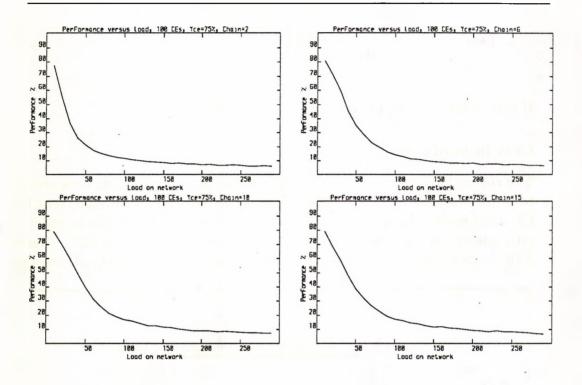

|   |            | 4.3.4 Results                                         |  |  |  |

| 4 | 4.4        | The performance of COBWEB                             |  |  |  |

|   | 4.5        | Summary                                               |  |  |  |

| 5  | Con   | nclusion                               | 143        |

|----|-------|----------------------------------------|------------|

|    | 5.1   | Communications for WSI                 | 143        |

|    | 5.2   | Formal Specification of Hardware       | 144        |

|    | 5.3   | Graph Reduction for WSI                | <u>144</u> |

|    | 5.4   | Further Work                           | 145        |

| Bi | bliog | graphy                                 |            |

| Α  | Сов   | BWEB as a TRS                          |            |

|    | A.1   | Directors                              | 153        |

|    | A.2   |                                        |            |

|    | A.3   | Primitives                             | 155        |

|    | A.4   | Data Constructors/Selectors            | 155        |

|    | A.5   | Sequencing, Strictness and Termination | 156        |

| в  | Сов   | BWEB in Paragon                        | 157        |

|    | B.1   | High level specification               | 157        |

|    |       | B.1.1 Packets and Agents               | 157        |

|    |       | B.1.2 Rewrite                          | 158        |

|    |       | B.1.3 Need                             | 159        |

|    |       | B.1.4 Fire                             | 159        |

|    |       | B.1.5 Wakeup                           | 159        |

|    |       | B.1.6 Reduce                           | 160        |

|    | B.2   | Transformed specification              | 173        |

1.1

\* \*\*

## Acknowledgements

This work was carried out in the Department of Computer Science at City University from 1986 until 1990, firstly in my capacity as a Research Assistant on the COBWEB project, and then as a lecturer in the department.

This work has been influenced by many discussions with colleagues and friends throughout the years. The greatest single influence has been that of my supervisor, Professor Peter Osmon. I wish to convey my heartfelt thanks to Peter for his help, support, and inspiration and for fostering and encouraging a lively research environment.

In addition, I would like to convey my thanks to the following, each of whom has been especially helpful.

Steve Ashcroft David Bolton Simon Croft Stephen Dedalus Hugh Glaser Chris Hankin Paul Kelly Malcolm Shute David Till Phil Winterbottom

My wife, Randi Kepecs deserves special recognition. As well as providing some of the original encouragement for starting this work, she lent her support and inspired confidence, especially during the darker periods of writing up. Finally, I would like to thank Noel and Phyll Anderson for their unwavering help and support for the last twenty seven years.

## Declaration

I grant powers of discretion to the University Librarian to allow this thesis to be copied in whole or in part without further reference to me. This permission covers only single copies made for study purposes, subject to normal conditions of acknowledgement.

7

## Abstract

This thesis addresses the problem of specifying, designing and implementing parallel computer architectures based on wafer scale integration (WSI). The requirements and constraints of WSI are considered and the class of computer architecture that is most suited to the technology is identified. This takes the form of a regular array of similar processors connected by a general purpose communications network. The communications function of the array is considered separately from the processing function.

Three routing algorithms for regular two dimensional arrays of processors are proposed. These are specified, and their properties are analysed. The performance of each of these is measured by simulation under varying conditions.

The problem of specifying and designing the processors is addressed next. A functional language engine is chosen as the target architecture. The processor specified and designed is a parallel graph reduction machine (named Cobweb) that uses directors as the instruction set. The programs executed on the machine are compiled from strictness analysed Hope<sup>+</sup> via FLIC to a director and parallelism annotated directed acyclic program graph.

A specification of a single processor, using a novel object-oriented parallel graph rewrite notation (named Paragon) is given. A methodology for translating Paragon specifications into a hardware design is given. This methodology is applied to the Cobweb specification. The resulting design is seen to be inefficient, so the specification is transformed, whilst retaining its semantics, to make it more efficient, and the translation process applied again. The resulting design has been simulated and some of the results from the simulator are shown.

The COBWEB specification is expanded to a multiprocessor one. Some of the problems in producing a specification for this type of machine are discussed. This specification is used to produce a design.

The results from a simulation of the multiprocessor COBWEB along with the results from the communications network chapter are used to predict the performance of a multiprocessor WSI graph reduction machine.

The thesis ends with a discussion of the merits and problems of specification and evaluation of this type of computer architecture. The communications architecture is found to be especially suitable for WSI; the specification and design tools are found to be sufficiently powerful, although limited in their scope. Finally the conclusion is drawn, with caveats, that WSI is a suitable technology for parallel graph reduction.

## Chapter 0

## Introduction

The recurring dilemma in the study of the design of computer architecture is whether raw speed is preferable to programmability. In traditional systems, this has been a simple tradeoff. However, as alternative programming paradigms and implementation technologies emerge, it is becoming more reasonable to expect speed as well as programmability. This thesis reports on an investigation into one way of achieving this goal. We attempt this by coupling two very different areas of computer science and engineering: Wafer Scale Integration (WSI) for the increased performance; and parallel graph reduction as an implementation technique for a class of languages with highly desirable features. In one line, the question that this thesis addresses is: "Is graph reduction feasible on a wafer?".

Inevitably, many other issues are raised as this question is addressed. Two of these become particularly prominent in this work. These are communications for WSI, and the formal specification and derivation of hardware.

### 0.1 Wafer Scale Integration

Since the advent of the integrated circuit, the method of manufacture has remained fairly constant. A large number of individual circuits are etched using photolithographic techniques onto a large slice of ultra-pure silicon known as a wafer. The wafer is then diced into "chips", and each is tested individually. Unfortunately, because of defects originally in the silicon crystal, or introduced at the time of manufacture, many of the circuits will be faulty and will not work. After testing, the working circuits are packaged and delivered, and the non-working ones are discarded. The principle idea behind WSI is that the entire wafer is packaged into a working product and sold.

The motivation behind moving to wafer scale integration can be summarised as follows. Basically WSI is

- cheaper -

- faster

- smaller

- more reliable

It is cheaper because the dominant costs in all phases of production are reduced. It is faster because slow off-chip communications are reduced. It is smaller because more components can be packed into a smaller space. It is more reliable, because there are fewer unreliable off-chip connections. These are compelling reasons, but the reason that WSI has not taken the world by storm is because of the scale and the difficulty of the one dominating problem. This is that the device must be guaranteed to work in the presence of the inevitable defects, ie it must be fault-tolerant.

In the past, this problem has proved so intractable that despite the obvious benefits of WSI, designers have opted to stick with tried and tested VLSI technology rather than attempt ambitious solutions to the fault-tolerance problem. As they have demanded increasing levels of integration and speed from their systems they have remained happy with their choice, because each new generation of VLSI component has consistently managed to deliver more performance over the previous. However, time is running out for VLSI. It is becoming much harder to extract yet more speed, and to make circuits even smaller.

What would a WSI device look like? Relatively vast areas of silicon are available, yet we know that a lot of circuits will be unusable because of faults. To get round this many circuits will be replicated, so that if one is faulty, another can be used instead. The replication may be at many levels, for example from extra rows and columns in a block of memory, to entire microprocessor blocks being replicated across the silicon. It is the latter type of system that we are most interested in.

At the same time WSI is offering substantial performance advantages over VLSI. The most dramatic of these is the vast increase in communications bandwidth between system components on the wafer. VLSI systems are limited by their off chip communications which tend to be slow, power hungry, unreliable, and limited by their physical size. However communications between blocks on a wafer do not have any of these problems. Very wide parallel data paths are fast, cheap and reliable.

Given such a system, where there are a large number of identical processors that can communicate with each other, we can separate the processor and communication function and consider each in turn. We call the processorcommunication pair a *node*.

### 0.2 Wafer Scale Communications

Communications on a wafer are not straightforward. The nature of the technology is such that long connections must be avoided, so the natural solution is one where each node can communicate with its physical neighbours only. Communications then take place as a number of steps from neighbour to neighbour. Communications between non-neighbouring nodes must then be via a set of intervening nodes. Of course, if a node is faulty, then it must be avoided. A suitable analogy is of an explorer in the dark equipped with a weakly powered lamp. The explorer needs to get from A to B as quickly as possible, and cannot afford to spend much time deciding where to go next. Unfortunately the way is made dangerous by patches of quicksand randomly placed in her way. The lamp allows her to see only a yard in front, but happily this is the length of her stride, so she can always avoid unwittingly stepping into the quicksand. However, this does not stop her from getting into a situation where she is totally surrounded by quicksand except for the way she came in. We provide three ways of allowing the explorer to complete the journey safely and in good time. The first is equivalent to planting a homing beacon on the destination, so that she can see the direction in which she should be going, and how far away she is. For the second, we provide a set of instructions at the outset in the form of "two steps forward, turn right, one step forward....". For the third, we provide a roadsign at each position that indicates "this way to your destination  $[\rightarrow]$ ".

Each method has its advantages and disadvantages. For example, method two will get her to the destination in fewer steps than method one, but if even one of the instructions in method two is wrong, then our explorer will end up anywhere but at the correct location.

Each of these methods has been designed as a communications algorithm for WSI, and we will discuss and evaluate each in turn.

## 0.3 Graph Reduction

Since the invention of the electronic digital computer, the dominating architecture has been the "von Neumann". This is the class of computer designs that consist of a single processor plus some memory, where the program that the processor runs is stored in the memory. The processor executes one instruction at a time, after which it computes where the next instruction to be executed is located. This class of computer was designed for the efficient execution of a particular class of languages known as the sequential imperative languages. Over the years designs have become highly optimised for this task, and present day von Neumann computers can now execute sequential imperative programs fast and efficiently. However, at the same time large programs written in the sequential imperative paradigm have become increasingly unwieldy. The problems of managing large programs with complicated relationships of components are immense. It is difficult to state that the programs match their specification, and they are expensive to maintain. This has led to the "software crisis" the realisation that programming large systems is difficult.

Many solutions have been proposed to deal with this problem. The one that is of interest to this thesis is the recognition that the underlying programming paradigm — the imperative sequential one is fundamentally unsuited to the requirements of constructing large software systems. There many other paradigms — the object oriented paradigm is one that has received most attention recently. However, the one we deal with in this thesis is the functional paradigm. In this paradigm, programs are expressed as sets of functions mapping input to output. As the functions are pure mathematical entities, the task of reasoning about programs is made much easier than with the imperative paradigm.

The paradigm has a hidden bonus — functional programs have the property that expression evaluation is guaranteed to be side effect free. This means that as a given expression will always evaluate to the same result, it does not matter when it is evaluated as long as it is safe to evaluate it in the first place. Many expressions can thus be evaluated concurrently. It is much easier to exploit hidden parallelism in functional languages than it is in the imperative paradigm.

Graph reduction is a technique for the execution of functional languages. In this thesis we present a formal specification for a graph reduction architecture and translate it into a hardware design. We prototype the design using a simulator, and we use the results from the simulator to predict the performance of a graph reducer.

## 0.4 Formal Specification of Hardware

As the level of integration of hardware has increased, hardware systems have become much more complex. In the past it has been acceptable to assert that a hardware design is correct simply because it has been tested thoroughly. However we have long been in the position where it is simply impractical to test hardware designs completely because the number of test input/output combinations has grown combinatorially with the complexity of the design. At the same time, users of such systems are placing increasing confidence in them, and are understandably becoming decreasingly tolerant of design faults. When a safety critical application has a component whose reliability cannot be guaranteed, then the usability of the entire system is brought into question. A proposed solution to this problem is the use of formal methods for hardware design. This way, designers hope to exclude design faults by deriving a design from a specification using rigorous mathematical techniques. Faults can then be proved absent rather than tested for presence.

There are various notations for formally specifying hardware. Unfortunately most of these are at a rather low level and express requirements in terms of physical hardware blocks with a specified topology and certain timing characteristics. As these are at such a low level, they make for fairly easy translation into hardware designs, and it is not hard to show that the design conforms to the specification.

However, there are higher levels at which we wish to express our requirements. For example if we require a system that behaves dynamically, one that grows and shrinks in size and capacity as demands are made of it, then instead of specifying it at a level which emulates the dynamicism, we would like a notation that allows us to express such behaviour directly. In this thesis we use such a notation. It allows us to leave the implementation of its behaviour to the system. Unfortunately this makes the process of producing a hardware design much more difficult. Eventually the design must be in terms of a physical hardware system, and as these systems cannot be physically dynamic such behaviour must be emulated.

We provide a route from this very high level requirements specification to a low level hardware design in terms of a number of logic circuits connected by wires.

### 0.5 Contribution

The main contribution of this thesis is threefold. Firstly, designs and performance results for a series of novel communications architectures for WSI. This work builds on previous work in [KS86]. Secondly, a formal methodology for transforming very high level specifications into hardware designs. This builds on the hardware specification language work of [BHK90]: Finally, some insight into the properties and problems of wafer scale graph reduction. This expands on some of the work done on the two Alvey COBWEB projects [HOS85, AHK+87, ABH+89].

### 0.6 Structure

The structure of this thesis is as follows. In chapter 1 we introduce the main subject areas of this thesis — wafer scale integration (WSI) and parallel architectures. We give the motivation for WSI and identify its major strengths and weaknesses. We introduce parallel architectures, and identify

the requirement that they be specified rigorously. We identify the type of architecture most suited to WSI. In chapter 2 we look at communication architectures for WSI and identify one which is especially good. In chapter 3 we give a full specification for a graph reduction architecture at a very high level, and propose a methodology for transforming such specifications directly into hardware. We apply our methodology to our specification and produce a prototype in the form of a simulator. In chapter 4 we estimate the performance of a parallel graph reducer on a wafer. Chapter 5 presents the conclusions, which in brief are that WSI is a suitable technology for parallel graph reduction.

16

## Chapter 1

# WSI and Parallel Architectures

The purpose of this chapter is to review the fundamental issues in the study of the two main subjects addressed by this thesis. The first of these is Wafer Scale Integration. The second is parallel computer architecture.

## 1.1 Review of WSI

Since the invention of the integrated circuit, the trend has been towards further levels of integration. From single transistors on a chip, we have seen an evolution to gates on a chip, to simple system functions, and on to entire microprocessors.

From early in the history of the technology the method of manufacture has been to etch many devices on a single wafer of silicon, dice the wafer into individual devices, test each device, discard the non-functional ones and package and deliver those that work. The idea behind WSI is that entire systems are fabricated on a single slice of silicon, and it is this slice that is packaged and delivered to a user.

There is a growing interest in WSI as reflected in the growing body of literature. [ST86, Lea87] report on two conferences on WSI. Later conferences have been held, but proceedings have not yet been published. [Tew89] is the definitive guide to the problems of implementing wafer scale systems. His introduction provides a readable overview of the subject. Two major projects in Europe and the UK have been investigating WSI. The Alvey project 073 is approaching completion. Its goal was to produce two technology demonstrators, one a non-regular signal processor, the other a regular SIMD image processing module. The ESPRIT 824 programme, started in 1986 aims to produce three technology demonstrators: a large RAM, a systolic array, and a highly fault tolerant microprocessor. There are two major approaches to WSI: the monolithic and the hybrid (or "jellybean"). The monolithic is where the device is constructed on a single slice of silicon. The hybrid approach is where diced chips are bonded directly onto the surface of the wafer. The wafer can then carry communications or memory. The scope of this work is monolithic WSI only.

The discussion will outline the issues involved in WSI, concentrating on those that are of relevance to the parallel computer architect. Physical implementation issues are beyond the scope of this thesis, although work in these areas will be referred to in many places.

#### 1.1.1 Why WSI?

As mentioned earlier, the reasons why WSI is a better technology than VLSI are as follows:

- It is faster

- It is more reliable

- It is smaller

- It is cheaper

- It is the natural successor to VLSI

In this section we will explain why the technology has these properties in the context of the differences between a WSI implementation of a system, and a VLSI version of the same system with the same functionality. That is, say we construct a system from VLSI from a number of discrete packages mounted on a PCB, connected to each other using PCB tracks. If we construct a functionally identical system in WSI, with each component written directly onto the silicon, and connected using on-wafer connections, then what are the properties of the WSI system compared to the VLSI implementation.

We will then discuss some of the problems associated with the implementation of wafer scale devices.

#### **Technology** Issues

WSI is in fact a fairly old idea, but has met with spectacular failures in the past, notably and infamously with the Trilogy project [Pel83]. This is not because the technology is fundamentally unsound, but is evidence of the difficulty of solving the related problems in the context of a rapidly expanding and vigorous VLSI industry.

Although WSI has been unsuccessful in the past, considerable progress has been, and is being made in addressing the problems that WSI raises. Much of this progress has arisen as the result of research into increasing integration for VLSI. WSI can thus be considered not as a radical departure from the conventional, but as another step, though in a different direction, in the evolution of integrated circuits.

VLSI has evolved with spectacular speed and has consistently delivered major performance and integration improvements from generation to generation. It has done so while many of the enabling underlying factors remain constant. However the evidence is that these underlying factors are approaching their fundamental limit.

Here we expand on the reasons VLSI is approaching its fundamental limit.

Feature Size. We have seen the continual shrinkage in the physical size of VLSI structures. The evidence is that the laws of classical digital electronics will not hold as devices get much smaller.

Feature sizes have been getting smaller at an exponential rate since the introduction of VLSI [Tew89]. State of the art commercial processes can now deliver chips with sub-micron devices. However the lower limit is expected to be about  $0.25\mu$ m.

As the feature size gets smaller, laws governing the behaviour of the devices break down. The statistical laws that normally apply simply cannot be relied upon when the number of charge carriers in a device gets small. Devices begin to behave non-deterministically, displaying behaviour that varies around an average.

As dimensions shrink, they begin to approach the physical dimensions fundamental to the classical analysis of electronic devices. Quantum effects come into play and also introduce non deterministic effects. Although there might be a place and an application for such devices, they are quite different from conventional electronic devices.

Integration We have seen increasing levels of integration. This has resulted from the decreasing feature size, but also from improvements in component density and packing efficiency.

Packing efficiency measures the fraction of silicon actually used for devices. Silicon is unusable due to the requirement for minimum separations between devices. The packing efficiency has been increasing, leading to a greater density of components on the silicon, but it will be difficult to increase packing density much further.

Chip Size Of particular interest to the study of WSI is the projected increase in chip size. Chip edge sizes have been increasing exponentially since the introduction of the technology [Tew89]. However as the chip size increases, it becomes increasingly difficult to make chips that are free of fabrication defects. The manufacture of VLSI devices has until recently relied on the presumption of perfection. If a device has a fault, no matter how small the defect that caused the fault, the entire device is discarded. This is becoming increasingly unreasonable. The system designer must provide for the component to function effectively in the presence of faults.

At the same time it becomes more and more difficult to test these chips as access to components located centrally through the peripheral connections is not easy.

We can see from the above that VLSI has almost exhausted every avenue available for increasing the number of components on a chip. The only avenue left is the one that increases the size of the chip, and which deals directly with new the issues implied. Thus there is a trend which will inevitably lead the study of VLSI towards WSI.

#### Speed, Reliability and Size

As well as offering increased levels of integration, the technology of WSI offers an increase in component connectivity which has implications on the speed of the system, its reliability, and its size. The number of pins on a package, and indeed in an entire system is a crucial limiting factor on VLSI systems for the following reasons:

- Connections from chip packages to PCBs are the most unreliable component of a system.

- Driving pins involves transforming the on-chip voltage and current levels to off chip levels, a process that consumes both time and power.

- VLSI packages are bulky compared with the chip itself.

These three reasons impose several limits on VLSI systems. First, the chip pin-out must be kept low so as to enhance the reliability. At the same time, the total number of connections in the system must be kept down, for the same reasons of reliability, and because of the physical space occupied by inter-chip connections. Second, the speed at which the chips are driven must be kept artificially low because they are physically distant from each other (compared with internal chip distances), and because driving pads at a high frequency incurs a high overhead in terms of power consumption.

WSI avoids the above problems because connections between circuits on a wafer are reliable, fast, and cheap to drive. Because the circuits are packed much closer together, they can be driven at a much higher clock rate, although for reasons given in section 1.1.2, it is not desirable for clocks to be distributed across the entire wafer. The greatest boon to the designer is that the level of connectivity between on-wafer circuits is much increased. Extremely wide parallel data paths are easily achievable at levels VLSI can never attain.

#### Economic Issues

The key question here is if a system designed from WSI components will be cheaper than an equivalent system designed from VLSI components. The cost of such a system can be broken down into five areas[Sum86]:

- Die cost includes the cost for processing the silicon, dicing the wafer into chips, and testing using probes.

- Component cost consists of packaging the device, and doing a final component test.

- Board cost consists the cost of the PCB the component is attached to, mounting the component on the PCB, and a test of the PCB.

- System Hardware cost will include the cost of connecting the PCBs together, cooling, supplying power, and the cabinet, and top level interface.

- Ownership cost includes the cost of maintaining the system throughout its lifetime. The factors that influence this cost are the system's reliability and "diagnosibility", and the cost of spares and services.

We consider each of the above in turn, and focus on the cost differences between a WSI system and a VLSI system.

Die cost The cost of a die is proportional to the number of working components that can be yielded from the wafer. Because we throw away all the non-working VLSI chips, the WSI approach is more cost-effective because we can (nearly) always yield a working device. With a WSI system, no dicing is done, and because testing is usually left until later, the amount of probe testing will be minimal.

Component cost The cost of a package for an integrated circuit is proportional to the number of pins. With a WSI system, only one device needs to be packaged. With a VLSI system the packaging cost is replicated for each component. Although the package for one WSI device will be more expensive than one VLSI package, the total cost will be less simply because the total number of pins will be less. **Board cost** The board cost is dependent on its sophistication, and the number of boards. A WSI system wins on both counts as higher integration leads to simpler boards and less of them. The cost of testing a PCB once the components have been mounted is proportional to the number of integrated circuit pins attached to the board. Again, the WSI system has the edge.

System Hardware Cost The cost of board interconnection, the cooling system, the power supplies, and the cabinet is directly proportional to the number of boards. As the increase in integration leads to fewer boards, the cost for a WSI system is less than for a VLSI system.

Ownership cost The cost of ownership includes the cost of services such as space, cooling, and power. As a WSI system will be physically smaller because it contains fewer boards, it will cost less in respect of space occupied. However the situation regarding cooling, and thus power consumption is less clear. The total cost of ownership is dominated by the maintenance costs for the system, and is thus proportional to the reliability of the system. The reliability of any integrated circuit is inversely proportional to the number of pins, as the connections to the PCB are by far the most unreliable component of any such system. So the WSI system wins again.

It is clear from this discussion that a WSI system offers substantial cost benefits over an equivalent VLSI system.

#### **1.1.2** Implementation Issues

The principal difficulty in the implementation of wafer scale systems is the avoidance of the inevitable faults. The problem is approached at a two levels: the circuit level, and the architectural level. Additional difficulties include testing, electrical design issues such as power distribution, and physical design issues such as packaging and cooling. Here we summarise these issues.

#### **Reconfiguration and Redundancy**

Given a circuit with a defect, there are three basic methods of working around that defect:

- 1. Physical repair including laser "zapping" to either cut connections and thus bypass the fault, or to add connections and enable the use of spare components.

- 2. Electronic switching using programmable switches.

- 3. Functional avoidance whereby a faulty circuit is simply ignored.

Each of the above methods requires some redundancy to be present. For the faulty block that is configured out, there needs to be a spare present to be configured in as a replacement. In some applications (for example memories) it may be possible to use the spares as well. Redundancy is a double edged sword however, as the discussion on yields will show.

#### Architectural Structures

A WSI architecture will typically consist of a number of circuits connected together using an interconnect. These can be characterised as having a *regular* or *irregular* structure. There will need to be some type of architectural reconfiguration mechanism to allow faulty units to be disconnected and replaced, or simply avoided. Standard reconfiguration techniques are explained in [NSS89].

**Regular arrays** The wafer scale device might take the form of a large number of identical or similar circuits replicated in a regular manner across the wafer. This might be so for several reasons. The application area might demand a regular architecture. For example systolic arrays demand an array of identical processors operating in lock-step. However, this has the requirement that the architecture must be made to look regular even though faults may have disrupted the physical layout.

Another reason for regularity is that the application might demand a large number of identical units, irrespective of their topology. In this case the application problem would be mapped on to a number of these units. In this case the physical layout is unimportant.

This class of WSI device requires some sort of interconnect structure exists to connect the elements together. Again there are several classes of interconnect, for example an architecture might only allow a circuit to communicate to its nearest neighbour, or the circuits might be connected in a tree fashion. Again the choice is very much application dependent.

Irregular structures A wafer scale device may simply be an extension of a VLSI type device where the entire silicon area embodies one function, albeit much more integrated. For example an entire CPU for a mainframe computer implemented in random logic. Faults are much less forgiving in this type of scheme — a small set of well placed faults can make the entire wafer unusable. This type of structure requires a much more sophisticated level of fault tolerance, and at several levels.

#### Defects, Failures and Yield Models

A defect is defined as a fault introduced at the time of manufacture. A failure is defined as a fault introduced after manufacture, typically appearing as the device is begin used in service. Defects are caused by imperfections in the manufacturing process. A wafer is manufactured from an ingot of silicon which has undergone extensive purification. However the process is not perfect, impurities are left behind and faults develop in the lattice structure of the silicon crystal. As the wafer is processed it is subjected to further stresses, such as impurities introduced by its chemical treatment, and thermal expansion and cooling. The lithography process whereby the wafer is etched may also be imperfect. Thus every wafer that is produced will have at least some faults on it. These faults are not distributed randomly. Analysis has shown that they are more likely to occur towards the edge of the wafer.

The yield Y of an integrated circuit manufacturing process is the fraction of working circuits to the total number manufactured. The principal problem with manufacturing large chips including wafers is that the yield decreases exponentially (or nearly so) with the area of the chip. Thus a whole wafer chip, with no fault tolerance has an infinitesmally small chance of working.

Early yield models were applied to VLSI processes with some success. The simplest model uses Poisson statistics and relates Y to the defect density D of a process and the area of the chip as follows:

$$Y = e^{-DA}$$

where D is measured in terms of the number of defects per unit area, and is a constant for the entire wafer. However this model is inappropriate for WSI in several respects. Firstly it takes no account of the fact that defects tend to cluster together, and that different types of defects have different tendencies to cluster. Secondly it does not address the fact that the defect density varies over the surface of the wafer, with the purest section around the center, and defects tending towards the edge.

More sophisticated models are sensitive to this clustering. [HS88] give the generalised negative binomial model. The yield of a circuit is dependent on the contributions of different types of defects. Each defect j has a coefficient  $\alpha_j$  that models its tendency to cluster. Higher values of  $\alpha$  indicate lower clustering, with unity indicating no tendency to cluster. The yield of a circuit that has area prone to fault j,  $A_j$  depending on a fault type j is given by

$$Y_j = (1 + \frac{D_j A_j}{\alpha_j})^{-\alpha_j}$$

and the yield of the entire cell  $Y_C$  where there are m types of fault is given:

$$Y_C = \prod_{j=1}^m (1 + \frac{D_j A_j}{\alpha_j})^{-\alpha_j}$$

Whichever model is used, it can be seen that the yield of a circuit is strongly dependent on its area. This has several important implications:

- A single large structure within a circuit may cause that circuit to yield unacceptably. This large structure is known as a *yield hazard*. For example long connections such as busses in WSI circuits are known to be significant yield hazards.

- The addition of fault tolerant circuits may have a deleterious effect on the yield. The extra area occupied may cause the entire cell to yield at a lower level than before. The net effect might be fewer working cells than if fault tolerance had not been attempted at all.

Recognition of the radial distribution of defects is important for WSI, as a designer can choose to place critical circuits near the center of the wafer, or the more robust circuitry towards the edge [HS88]. This is modelled using the generalised negative binomial model by making D a function of the distance from the center of the wafer.

#### Testing

As fault tolerance is of prime importance to WSI, testing of all circuits is necessary so that the non functional ones can be configured out. Testing can be performed either internally, or externally. Internal testing techniques allow the circuits to test themselves or each other. A common technique is to wire in a test circuit that generates a "signature" only if all the components of the circuit are working correctly. The correct signature can be generated during the design phase using simulation and can be hard-wired into the testing circuitry for comparison. This technique is known as *signature analysis*.

External techniques usually take the form of generating test vectors, applying them to the inputs, and checking if the outputs are correct. The number of test vectors required to rigorously test a circuit increases rapidly with the number of inputs, so the number of test vectors for a WSI device is expected to be unreasonably large. It is therefore necessary for test circuitry to be built into the device so as to minimise the amount of external testing.

One technique for testing WSI systems is to have a configuration phase when the device is powered up. This will consist of initiating internal test sequences and constructing an external view of the wafer that indicates where the faulty areas lie. This map can be used for several purposes, for example to switch in spare circuitry, or configuring the communications so that the faulty areas can be avoided.

#### Electrical and Physical Issues

Electrical issues include the distribution of power and signal. Signal distribution is particularly difficult as clock skew is an unwanted effect associated with distributing signals along long wires. A global clock is needed when all the circuits on the wafer need to operate synchronously, such as in a systolic array to give a regular example, or in a large processing unit. However more liberal architectures will operate asynchronously, so the signal distribution problem can be avoided.

Power distribution has not been identified as a major problem by any of the workers in the field [WL87], although it is important to be able to isolate power shorts. The major physical implementation issue is packaging which comprises mounting, and heat dissipation. [ML86] shows that WSI packaging is not simply an natural extension of VLSI packaging, assuming SIMD processors. [Pit87] proposes some methods of cooling WSI devices. The amount of heat generated is very application dependent. For example the Anamartic wafer memory product generates so little heat that it does not even need cooling fins.

### **1.2** Parallel Architectures

Since the invention of the electronic digital computer the dominant design has been the "von Neumann" architecture. This architecture is characterised by a single processor executing a program which stored in a linear memory along with the data required for running the program. The model was designed for, and is particularly suited to running a class of programs known as sequential imperative programs.

However it is becoming evident that the premises on which the architecture is based, ie: "imperative" and "sequential" are limited. Imperative languages have been blamed for the "software crisis" — a phenomenon whereby the dominant cost in the production of most software is maintenance. At the same time, as increasing performance is demanded from computer systems, the single processor model is being being abandoned in favour of the multi processor.

The multiprocessor model also demands a different model of computation. Here there is a mismatch between the nature of the imperative paradigm, and this new model of computation. That is, it is difficult to program imperatively so as to exploit parallelism. Again a promising solution to the problem of efficiently exploiting parallel architectures is a different programming paradigm, where parallelism does not need to be made explicit.

More recently, as alternative programming paradigms have come to the fore, it has been realised that the von Neumann architecture has some fun-

damental problems executing such programs efficiently. The cause that has been identified is the memory bottleneck. This is a term that is used to describe the single narrow access point to the memory, and the mismatch between the speed of the processor and the relative sluggishness of the memory.

#### **1.2.1 Specifying Parallel Architectures**

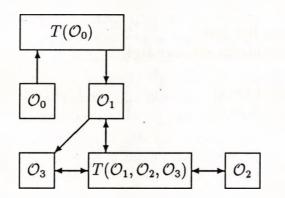

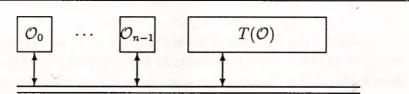

If we are to implement a parallel architecture, we first need to be able to specify it. Also, once we have a specification, we need to be able to transform that specification into a design. Specification is a hierarchical process. We start from requirements and move through stages of adding increasing detail and constraints until we arrive at a design that is capable of being implemented. As we progress through the stages we would like to be able to assert with confidence that certain properties remain invariant

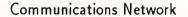

For example the stages in specifying an parallel architecture might be as follows [BHK90]:

- 1. High level requirements statement, known as the logical model.

- 2. The systems architecture, which specifies logical processes and communications between these processes.

- 3. The processor architecture, where the logical processes are mapped onto virtual processors.

- 4. The physical architecture, where the virtual processors are mapped onto physical processors with associated memory and communications medium.

The top level requirements statement should be in a language close to the problem domain. However the process of getting down to the physical level is not easy. Some of the problems are elucidated in [BHK90].

The problem of formally specifying hardware has been studied extensively. Gordon at Cambridge has proposed a specification system based on higher order logic [Gor86]. Inmos have specified a hardware floating point unit for the Transputer [MK87]. The specification was originally written in Z, and transformed to OCCAM and then compiled into silicon.

However the specification of hardware systems that consist of a number of concurrently active agents, and especially those that communicate asynchronously and are dynamic, poses special problems. Several teams have proposed languages in which to specify this kind of architecture. DACTL [GKS87] and Lean [BvEG<sup>+</sup>87] are languages based on term graph rewriting. FP2 is a language based on term algebras for transition systems [SJ89]. AADL is an axiomatic specification language [DD89], with behavioural specifications expressed in an extension of CSP.

### **1.3** Summary

In the light of the technological requirements and constraints, we can recommend a particular kind of parallel computer architecture as well-suited to WSI.

This takes the form of a regular array of similar processors connected to a general purpose communications network. The communications architecture consists of a number of communication processors which communicate with their nearest neighbours only. Each processor operates asynchronously. Fault tolerance is handled mainly at the architectural configuration level, and each processor has some built in test circuitry. A configuration phase at power up time will arrange for the network and the processors to be tested both internally and externally by a controller. This controller will contain information about the status of the wafer, eg the location of working processors.

We choose a regular array because this is easier to yield than a nonregular architecture. We choose a general purpose communications network so as not to pin down the nature of the processor at too early a stage. So as to minimise yield hazards caused by large structures such as long busses, we permit nearest neighbour communications only. Because of the problem of distributing clock across the wafer, we will allow the processors to operate asynchronously relative to each other.

As the processor will replicated across the wafer, and because we cannot guarantee a regular topology, the processor most suited to this kind of architecture will be one that can operate concurrently with others, and which does not require a regular topology, or synchronous communications. The processor that we choose will be specified formally using a notation that allows us to express requirements at a very high level.

## Chapter 2

## **Communications for WSI**

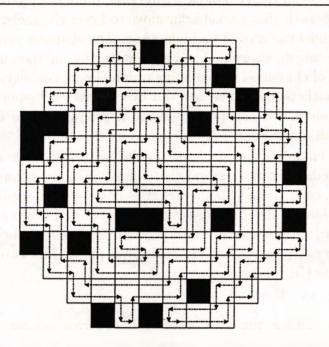

In chapter 1 we concluded that the type of architecture most suited to WSI is one that is a regular array of similar processors connected by a general purpose communications architecture. In this chapter we present several communications architectures that match these requirements, and are independent of any specific processing element.

To aid in the analysis of these architectures we first introduce some terminology and metrics, and identify the requirements of a WSI communications architecture over and above those of a more general purpose communications architecture. We proceed with a review of other communications architectures for WSI. Finally we present three new designs. The designs are presented in historical order of conception, rather than in order of merit. For each design we say how it meets the requirements and estimate its performance in terms of the metrics defined in section 2.1.

In several sections we present results that have been calculated using a simulator. These results are generated by creating models of typical wafers at random, and measuring their properties. The location of faulty CEs on these synthetic wafers accurately reflects the radial distribution of defects found in real wafers [HS88].

## 2.1 Terminology, Metrics & Requirements

#### 2.1.1 Terminology & Metrics

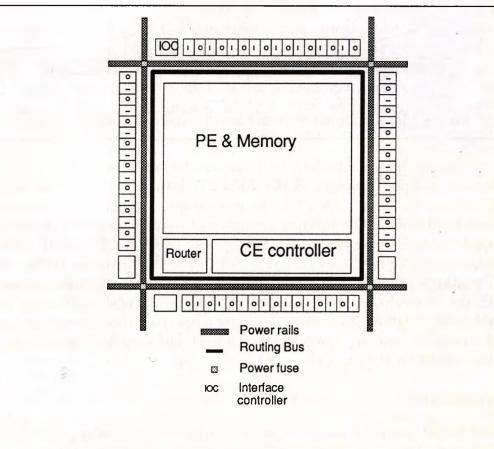

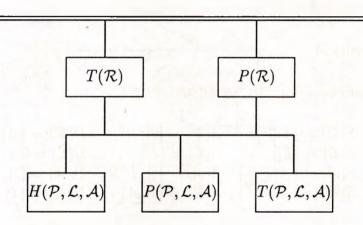

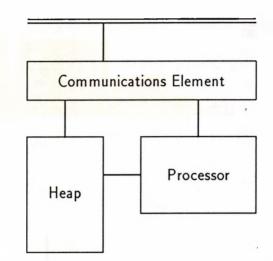

As explained earlier, the class of WSI computer we are studying here consists of a regular array of processors connected by a communications network. Each processor is connected to the communications network, and the processor-connection pair is called a *node*. A node can be thought of as a communications element (CE) connected a processing element (PE). Ideally, the CE and PE are independent of each other, though this is not always the case in implementation.

Two types of network are of interest — packet-switched or store-andforward, and circuit switched. Processors communicate messages across the network. In a packet-switched network, units of communication are called packets which for this design will be units of 128 bits. Messages are then sent as a series of one or more packets. A communications step in a packetswitched system consists of the complete transfer of a packet from one node to another. This is known as a hop. In order to complete a communication from a source node to a destination node the packet must perform a number of hops via a series of intervening nodes. In a circuit-switched network, messages are broken up and sent in pieces from a source to a destination over a path that is fixed and held open for the duration of the communication.

In order to be able to compare different communications networks we need to be able to describe these networks in terms of a number of network terms and metrics. These are introduced here. Some of these are specific to WSI.

**Connectivity** is defined as the maximum number of nodes any given node can be directly connected to. For example, a mesh type architecture, where each node is connected to nearest four neighbours only, has a connectivity of four.

Routing algorithm. A communications network I is a directed graph I = G(C, N) where N represents the set of nodes and C represents the set of communication channels or links between nodes. A particular channel is denoted  $c_i$ , and an individual node is denoted  $n_i$ . Routing functions determine where to route individual packets. Routing functions are denoted by a type, eg:  $\mathcal{R} : N \times N \mapsto C$ , that is a function that takes the current node and the destination node, and produces the channel on which to forward the packet. A routing function or algorithm is said to be correct if it correctly routes a packet from its source to its destination in a finite time.

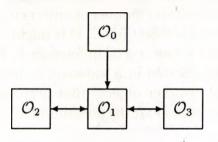

**Deadlock freeness.** One of the fundamental requirements of any routing algorithm is that it be deadlock free. There are various ways of ensuring that any particular algorithm is deadlock free, and these are reviewed for different networks in the context of WSI in section 2.3. Deadlock occurs when a set of processes is blocked because each is waiting for the exclusive use of a resource which is held by one of the other processes in the set, and where no process can back off.

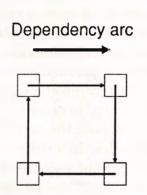

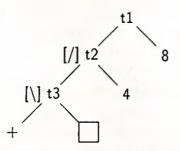

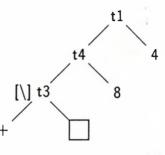

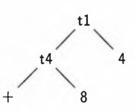

Deadlock occurs in packet switched communication networks when there is a cycle of dependencies in the packet buffer dependency graph. Figure 2.1 shows an example of how deadlock might occur in this manner. Deadlock

avoidance strategies in general involve either breaking the dependency graph when it forms, or ensuring that it can never form in the first place.

**CE/PE binding.** A CE and a PE are logically independent blocks. In principle a PE may be connected to a number of CEs. However a PE will not in general be usable if its CE, or set of CEs do not work. A CE on the other hand will generally be usable if the PE is faulty. A PE is tightly bound to its CE (and vice versa) if the functionality of each is dependent on the other. The elements are loosely bound if the CE can work independently of the functionality of the PE. Obviously it is more advantageous in terms of functionality if the elements are loosely bound, and can work independently. Some architectures however are such that they are tightly bound.

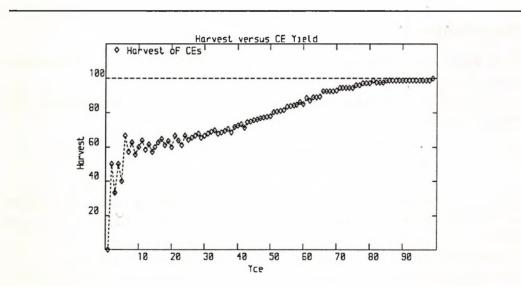

Harvest/Sacrifice. A given CE/PE design will have a yield denoted  $Y_{CE}$  and  $Y_{PE}$ . Some CEs will be in strategically important positions on the wafer such that if these do not work, then they will cause other nodes to be unreachable, that is, the only communications to them is broken. The Harvest H is defined as the proportion of working nodes that can actually be used. H is of course sensitive to  $Y_{CE}$ . Usually there is a certain value of  $Y_{CE}$  at which H becomes unacceptably low. This is known as the Yield cutoff point  $Y_{Cutoff}$ .

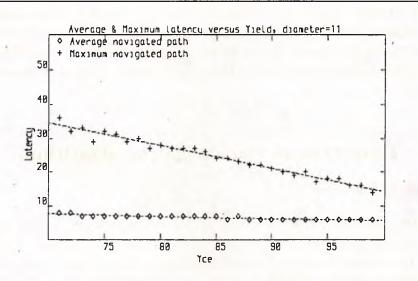

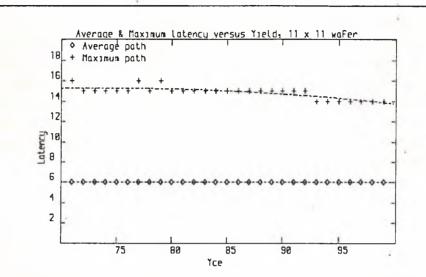

If the elements are loosely bound then some PEs will not be usable because their CEs will not be working. These PEs are said to be *sacrificed*. Also, some nodes may be working, but unusable because there are no communication paths to them. These are also said to be sacrificed. Latency l is defined as the amount of time taken between dispatch of a message by a sender, and its complete receipt at the destination. A given network will have an average latency  $\overline{l}$  and a maximum latency  $l_{\max}$ . The average latency is defined as the average time taken to communicate a message between a source and a destination chosen at random. The maximum latency is defined as the time taken to communicate between the two furthest removed nodes.

**Performance.** The performance of a network can be defined fairly loosely as how it behaves in terms of metrics such as latency as certain parameters are varied. Parameters of interest include yield, and load. For example if the load rises, this can lead to increased congestion, and the latency might increase.

**Overhead** is defined as the amount of information in addition to the payload, a message must carry in order to complete successfully. This usually includes the destination address.

#### 2.1.2 Requirements

The requirements of a communications network for WSI are a superset of the requirements of a general purpose communications network, that all messages must be guaranteed to get to their destination within a finite time. A corollary of this is that the network must be deadlock free.

WSI introduces some other requirements. The most important of these is that the communications node must be sufficiently small and simple to allow it to yield well. That is:  $Y_{CE} > Y_{Cutoff}$ . A second requirement is that a WSI communications architecture must be fault tolerant. That is it must be able to guarantee delivery of messages in the presence of faulty nodes. This may involve a configuration phase either when the WSI device is fabricated, or at power on time when CEs are tested and, if necessary, informed of the state of their neighbours.

#### 2.2 Review

There have been a number of studies of communications networks for WSI. This section reviews two of interest.

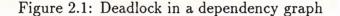

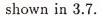

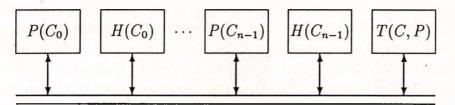

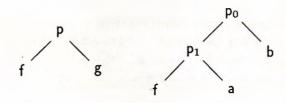

In the context of regular WSI communications networks, figure 2.2 shows the convention for illustrating the functionality of nodes.

#### 2.2.1 Catt's Spiral

Catt's Spiral was one of the original communications networks for WSI. It was proposed as a method for configuring working processors in a highly regular array [AC78]. It has had some success. The Catt spiral has been used in several designs for WSI machines. Cobweb-1 [Shu83, Kar87] used the spiral as its communications network. Anamartic Ltd. manufacture a wafer memory device using the Catt spiral [Cur89].

The spiral is basically a string of nodes linked together, usually starting from an node close to the edge of the wafer. Each node on the spiral is identified by an address which is relative to the start of the spiral. To communicate with another node the packets are sent along the spiral in the direction dictated by the difference between the current node address and the destination node address. In the context of the spiral, this is known as *serial* communication. Alternatively packets can be transmitted *radially*, that is a packet can go from an outer shell of the spiral to an inner one in one hop. At power up time the wafer controller initiates a test and configuration sequence which arranges for the nodes to be tested and working ones configured into the spiral.

The spiral is grown from a single node close to the edge of the wafer. This means that a number of external devices wishing to access the wafer must contend for access to this port. Any communication to the outside world must also go via this port.

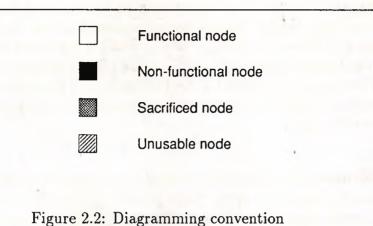

Figure 2.3 shows an example four-connected wafer configured as a spiral. There are no dud CEs on this example wafer.

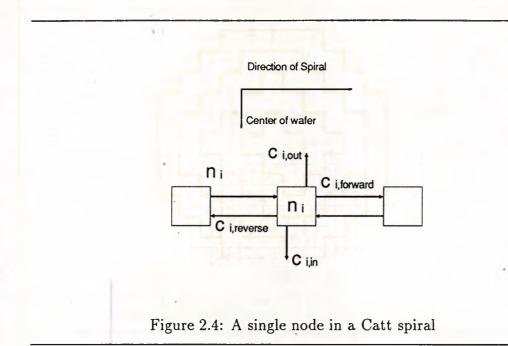

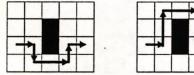

Figure 2.4 shows a typical node  $n_i$  with its connections to the nodes in the "forward", "backward" and "in" and "out" directions.

Figure 2.3: A wafer configured as a Catt spiral

#### Characteristics

**Connectivity** The standard Catt spiral with no radial routing has a connectivity of two. However with radial routing, the connectivity goes up to four. The spiral can also been proposed for wafers with connectivity six and eight [Shu83], although because eight does not tessellate, some tricky electronics are involved.

Routing algorithm The best thing that can be said about the spiral is that the routing algorithm is so simple that it is extremely easy to implement in hardware and as a result it is very fast. For the simple non-radial case each node has a forward connection and a reverse connection to its neighbours in the spiral. Each node has an address such that nodes near the start of the spiral have low addresses and those towards the end have high addresses. The routing algorithm is then as follows: given the address of the current node and the address of the destination node it returns the channel on which to forward the packet.

$$\mathcal{R}_{\text{Catt}} : N \times N \mapsto C$$

$$\mathcal{R}_{\text{Catt}}(n_i, n_d) = \begin{cases} c_{i,\text{forward}} & \text{if } i < d \\ c_{i,\text{reverse}} & \text{if } i > d \\ c_{i,\text{home}} & \text{if } i = d \end{cases}$$

(2.1)

When there are radial connections the routing algorithm is more complex. As well as having links to the forward and reverse directions, the node must also have links to, and know the address of the nodes towards the center and

towards the edge of the wafer. These new directions are called "in" and "out" respectively. Of course some nodes will not have links in these directions if they are either on a corner of the spiral, or are next to a dud node. To describe this algorithm we need to define the function  $link : C \mapsto N$  which takes a channel and returns the node that is connected to that channel (if one exists). This new routing algorithm is as follows:

$\mathcal{R}_{\text{Catt}} : N \times N \mapsto C$   $\mathcal{R}_{\text{Catt}}(n_i, n_d) = \begin{cases} c_{i,\text{home}} & \text{if } i = d \\ c_{i,\text{in}} & \text{if } i < d \land x \leq d \\ c_{i,\text{forward}} & \text{if } i < d \land x > d \\ c_{i,\text{out}} & \text{if } i > d \land y \geq d \\ c_{i,\text{reverse}} & \text{if } i > d \land y < d \end{cases}$ where  $n_x = \text{link}(c_{i,\text{in}})$   $n_y = \text{link}(c_{i,\text{out}})$  (2.2)

**Deadlock** The Catt spiral is naturally deadlock free. This is because a packet is routed either in the directions forward and in or the directions out and reverse. Routing is essentially unidirectional. The cycle of dependencies can thus never form.

Harvest & Sacrifice One of the main problems with the Catt spiral is the fact that in its simplest form, not all nodes can be configured for use, even

12

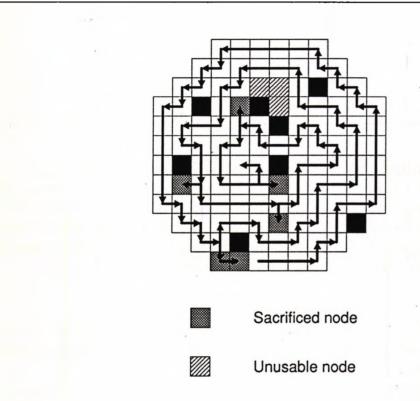

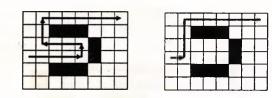

though they are working perfectly and they have perfectly working neighbours. This is because there are situations where the spiral advances into what are termed "blind alleys" — positions from which it cannot continue. It must then backtrack and sacrifice the nodes along this section. Figure 2.5 shows an example of a wafer on which several nodes are sacrificed because they are in a blind alley some nodes are sacrificed because the spiral cannot use them.

Figure 2.5: Catt spiral sacrificing several nodes that are in "blind alleys", and ignoring others that are unconfigurable.

This means that the harvest of working nodes is far from perfect.

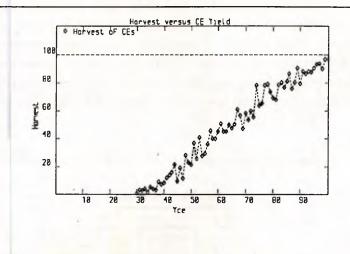

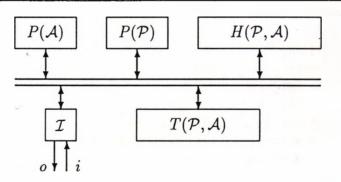

Another problem with this is that  $Y_{\text{Cutoff}}$  is fairly high. So in order for it to work, the designer of the CE must ensure that  $Y_{\text{CE}}$  is high. Figure 2.6 shows the results of the simulation of the harvest given by the Catt spiral against  $Y_{\text{CE}}$ . It can be seen from this that the harvest is far from ideal. Here we see the communications architecture dictating which PEs are usable. The purpose of the CE is to serve the processors, not limit them.

Figure 2.6: Harvest versus Yield for Catt spiral

**CE/PE binding** Some of the original designs using the Catt spiral were such that the CE and PE were tightly bound [Shu83]. This was because the PE address was the same as the CE address. If the PE did not work, then the CE could have no logical significance in the spiral, therefore it would be sacrificed, despite working perfectly. However, later COBWEB designs and the Anamartic wafer memory have the PE loosely bound to the CE.

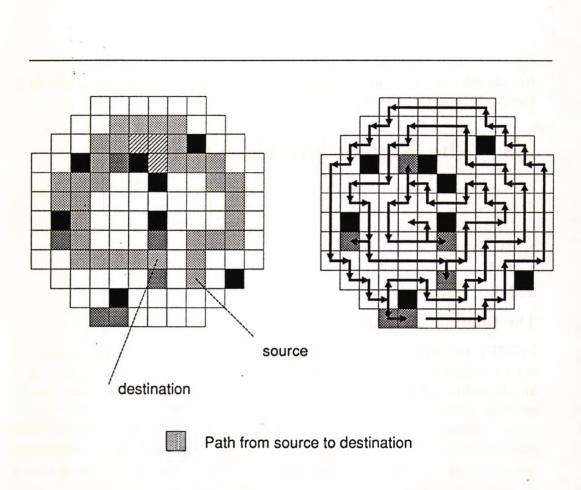

**Latency** With the simple Catt spiral with no radial connections, if there are x nodes configured into the spiral, then the average latency is proportional to half the length of the spiral:  $\overline{l} \propto \frac{x}{2}$ .

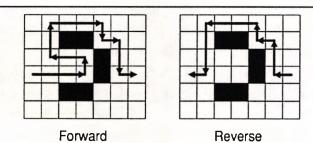

With radial connections the latency is proportional to the dimension of the wafer:  $\overline{l} \propto \sqrt{x}$ . The Catt spiral has a fairly high average latency compared to the average physical distance between nodes. Consider the example in figure 2.7. The figure to the right shows path of the spiral, and to the left the route taken by a packet. The packet must go all the way round the wafer before it can get to its destination even though it is physically fairly close. This is true even for a wafer with radial connections.

**Performance** The Catt spiral is essentially a serial configuration mechanism. Although there may be many packets in flight at once in the machine, they must all be travelling along the spiral, or along radial connections, with the majority travelling along the length of the spiral. Queues inevitably build up along the spiral and lead to congestion. The performance does not respond well to increasing congestion [AO88].

Figure 2.7: An unnecessarily long route taken by a packet following the spiral

#### 2.2.2 Other networks

#### Tree networks

Some teams have identified tree networks as the basis of possible communications architectures. Lea at Brunel University has developed the WASP architecture for image processing based on string processors [JHL90] which is based on a tree architecture. Brunel WASP is a radically different architecture from the main subject of this thesis in that it is SIMD, and thus operates synchronously, and requires a fairly regular physical topology. This topology is achieved by linking a number of processors into "branches" around a central "trunk". The branches then link together to form a "string". Thus it is not subject to all of the terms and metrics described in section 2.1.

Although the team have had some success with the approach [JHL90], the communications network is not recommended for all applications. This is because a badly placed fault in the structure of the communications network can have disastrous consequences. For example, if a node close to the root of the tree fails, this can potentially cut off all the nodes on the other side of the branch, and thus waste many good nodes even though they might have many working neighbours.

## 2.3 The Navigation Algorithm

As mentioned in the introduction the architecture for which this algorithm is defined is a highly regular packet-switched communications architecture. All nodes are identical except for a number of I/O nodes close to the boundary of the wafer.

#### 2.3.1 Routing

#### The Routing Algorithm

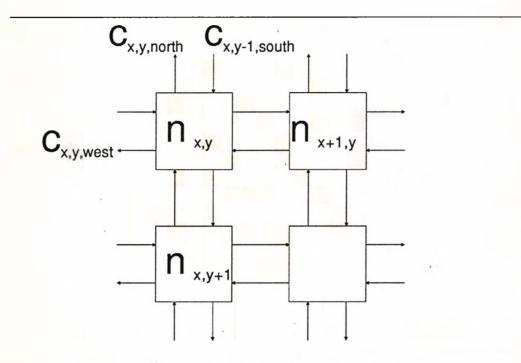

In order to achieve communications between non-neighbouring nodes, we need a communication algorithm. To take a first step towards finding such an algorithm, let us imagine a perfect wafer where everything works totally reliably. Each node on this wafer is fully connected to its four nearest neighbours. We can think of this wafer as a two-dimensional mesh. Each node has a location in the mesh which can be written as the cartesian co-ordinates of that node in the mesh relative to some origin. Each node has a set of channels linking it to its neighbours. These can be envisaged as a set of directions  $D = \{north, east, south, west, home\}$  as in figure 2.8.

A simple communications algorithm can be devised based on this addressing system. The routing function is shown below. This function maps the current node and the destination node onto the channel on which to forward the packet. It is a simple matter to prove this correct. For each hop, the packet is routed to a node closer to its destination. As long as the path is not blocked, the packet is guaranteed to be delivered.

$$\mathcal{R}_{\text{Nav}}: N \times N \mapsto C$$

$$\mathcal{R}_{\text{Nav}}(n_{x,y}, n_{xd,yd}) = \begin{cases} c_{x,y,\text{home}} & \text{if } (x,y) = (xd, yd) \\ c_{x,y,\text{north}} & \text{if } y > yd \\ c_{x,y,\text{south}} & \text{if } y < yd \\ c_{x,y,\text{east}} & \text{if } x > xd \\ c_{x,y,\text{west}} & \text{if } x < xd \end{cases}$$

$$(2.3)$$

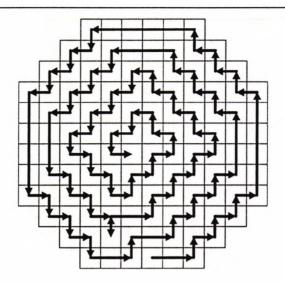

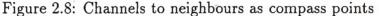

However, things are not so simple on a real wafer. The perfect mesh assumed for this routing algorithm is inevitably disrupted by defects. Any routing algorithm for WSI must take account of these defective areas and cause the packet to avoid them. Of course these areas can be arbitrarily complex. Figure 2.9 shows a particularly nasty wafer.

In a wafer that does form a perfect mesh, the routing algorithm above is sufficient. Indeed, there will be regions of a non-perfect wafer where this

routing algorithm will work. However, when there are defective areas, this naive routing algorithm leads packets into areas from where they cannot progress closer to their destination. The packet cannot backtrack, because the routing algorithm would take it right back to where it got stuck, leading to a livelock situation.

The strategy we adopt is to let a packet know when it is blocked from further progress and to let it then take evasive action. To implement this, the packet must operate in two modes. We call these blocked and unblocked modes. This algorithm has some origins in the cartesian routing algorithm mentioned in [KS86]. However that algorithm requires CEs to be sacrificed using convex wrapping so that "concavities" in areas of faulty CEs can be filled.

The routing algorithm for when the packet is unblocked is simple and is based on the previous routing algorithm with a minor modification. The modification is based on the observation that at some points in the mesh, the packet can move in more than one direction to get closer to its destination. For example if a packet is on the south-western diagonal, it can go either north or east. The modification to the routing algorithm is as follows: If the packet cannot move in the optimal direction, it will be routed in one of the less optimal directions. This relies on any particular channel knowing whether or not it is connected to a working CE. The predicate  $dud : C \mapsto \{T, F\}$ indicates if a particular channel is connected to a non-working CE.

Figure 2.9: A pathological arrangement of faults on a wafer

The formal definition of the routing algorithm with the modification is given below. It is easy to prove that this routing algorithm is correct. Again, each step routes the packet closer to its destination.

$$\mathcal{R}_{\text{Nav}} : N \times N \mapsto C$$

$$\mathcal{R}_{\text{Nav}}(n_{x,y}, n_{xd,yd}) = \begin{cases} c_{x,y,\text{home}} & \text{if } (x,y) = (xd, yd) \\ c_{x,y,d} & \text{if } \neg dud(d) \end{cases}$$

where

$$d = \begin{cases} \text{north if } y < yd \\ \text{south if } y > yd \\ \text{west if } x < xd \\ \text{east if } x > xd \end{cases}$$

$$(2.4)$$

As defined here, this is non-deterministic. If a packet can go in one of two directions, say north *and* east, then either can be chosen. However, the hardware to implement such a routing algorithm would be deterministic and would choose one direction in preference to the other.

If the packet cannot move in any direction that would take it closer to its destination, then it becomes blocked. At the time it becomes blocked the packet is effectively facing a wall of dud nodes. The purpose of the routing algorithm is to move the packet into a position where it can become unblocked and thus resume moving closer to its destination.

The condition that the packet will become unblocked when it is closer to its destination than it was when it became blocked, is essential if we are to prove that the routing algorithm works. If we can prove that when the packet is blocked the routing algorithm manoeuvres the packet closer to its destination then we can be sure that the routing algorithm is correct.

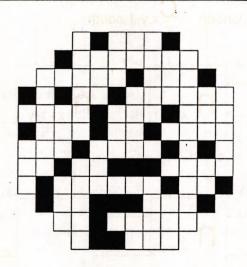

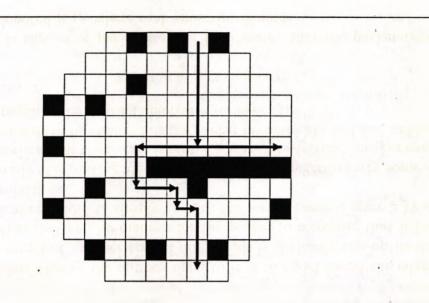

Figure 2.10: The routing algorithm in full action

In fact, getting into such a position is quite easy. All the packet has to do is to follow the edge of the area of duds. This is guaranteed to bring it closer to its destination. Figure 2.10 illustrates the action of the algorithm in the blocked phase.

There is an important optimisation that can be made to the algorithm. Consider the action of the algorithm when it encounters the physical edge of the wafer. One of the options open to it is to crawl round the edge as if the edge were just another area of duds. This is obviously non-optimal. The optimisation that can be made is for the packet to recognise that it has hit the physical edge and to simply go back the way it came. Figure 2.11 shows this optimisation.

Obviously this routing algorithm requires the packet to carry some state. which can change as the packet is routed towards its destination. For example the mode needs to be changed as the packet becomes blocked and unblocked.

This requires the routing algorithm to be of type

$$\mathcal{R}: P \times N \times C \mapsto P \times C$$

where P is the set of packet states. The "state" that the packet needs to carry is denoted  $p_{s,b,h}$  where each subscript denotes

Figure 2.11: Packets "bouncing" off the edge of the wafer

- A displacement field 0 < s < maxs where maxs is a constant whose value is greater than the distance between the two furthest removed nodes on the wafer

- A blocked bit  $b \in B = \{T, F\}$

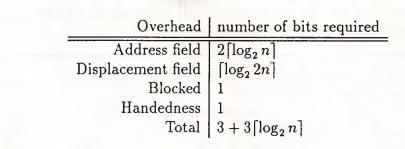

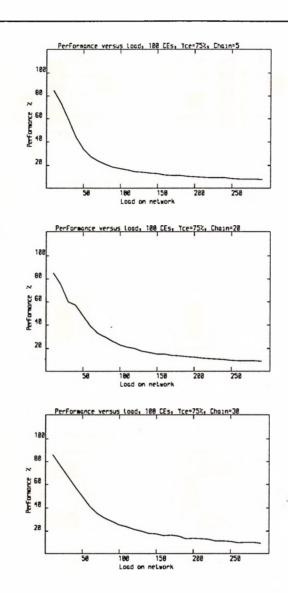

- A handedness bit  $h \in H = \{L, R\}$