**City Research Online**

## City, University of London Institutional Repository

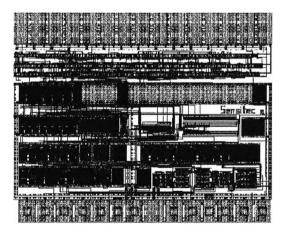

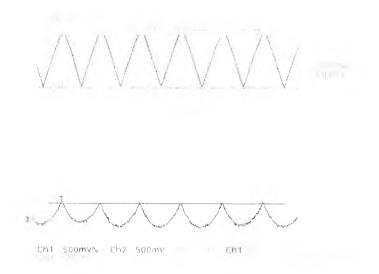

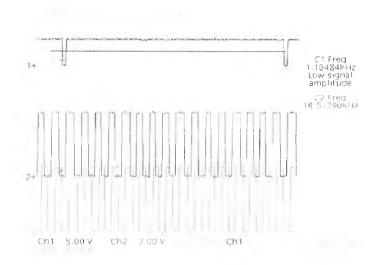

**Citation:** Leitis, K. (2004). Analogue hardware based algorithm for low-power and lowvoltage position measurement systems with enhanced resolution. (Unpublished Doctoral thesis, City, University of London)

This is the accepted version of the paper.

This version of the publication may differ from the final published version.

Permanent repository link: https://openaccess.city.ac.uk/id/eprint/30681/

Link to published version:

**Copyright:** City Research Online aims to make research outputs of City, University of London available to a wider audience. Copyright and Moral Rights remain with the author(s) and/or copyright holders. URLs from City Research Online may be freely distributed and linked to.

**Reuse:** Copies of full items can be used for personal research or study, educational, or not-for-profit purposes without prior permission or charge. Provided that the authors, title and full bibliographic details are credited, a hyperlink and/or URL is given for the original metadata page and the content is not changed in any way.

City Research Online:

http://openaccess.city.ac.uk/

publications@city.ac.uk

Analogue Hardware Based Algorithm for Low-Power and Low-Voltage Position Measurement Systems with Enhanced Resolution

> by Karsten Leitis

Thesis Submitted for the Degree of

DOCTOR OF PHILOSOPHY

CITY UNIVERSITY LONDON Department of Electrical, Electronic and Information Engineering

August 2003

# Abstract

Position measurement systems are used in a wide variety of applications based on different sensing principles. Whatever the application or sensing method, they all share common issues of accuracy, robustness and power consumption. This thesis concentrates on two aspects of sensor interface design in order to achieve a very low power consumption for position measurement systems, in order to optimise their use for battery applications.

A new architecture and optimized components have been investigated with regard to low power and low voltage operation. The architecture establishes typical properties of position measurement systems such as linearization and resolution enhancement. A new method for resolution enhancement in respect of low power and low voltage system requirements is proposed within this work. The same major requirements are also fulfilled on a component level.

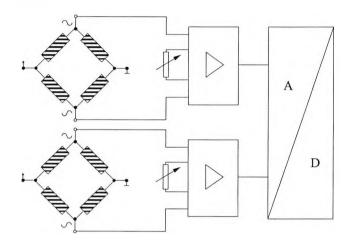

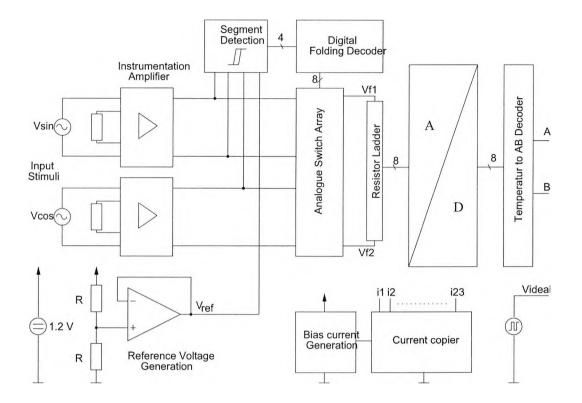

On an architectural level, the method utilizes signal symmetry provided by the sensor signal. A very common output signal of position measurement sensor elements establishes a sine and a cosine waveform. With folding and signal transformation techniques these signals are coarse converted and preprocessed before A/D conversion. As a result, the number of components is reduced and a significant amount of power is saved.

Many position measurement systems linearize the sensor element signals by digital computation. This work proposes a method of linearization within the A/D converter. The advantage is that no extra power consumption is involved because no additional elements are inserted into the A/D converter. By using a non-linear resistor network that composes the sine and cosine sensor signal, a linearized output is obtained. As a result the linearization algorithm is realised by an analogue hardware circuit. This has the added benefit of reducing the circuit noise, a common problem with digital circuits.

In addition to the architectural level design, new components realized as integrated circuit cells, contribute to a reduction of the overall power consumption. Both, the power supply voltage and the power supply current are significantly reduced. A trade-off between performance and reduction of power consumption has been the basis of the circuit design. Circuit components that determine the minimum power supply voltage have been the subject of a thorough investigation in respect of sub-threshold or moderate inversion operation. As a result, a power supply voltage range smaller than given by the fundamental limits for strong inversion operation can be chosen. These components were realized as a physical cell design and implemented in the form of a test chip. Test results are reported that demonstrate the practical performance of the overall architecture and individual components.

A new error model has been developed for the overall sensor system in order to investigate the influence of parameter deviation and inherent errors. The model has been used in simulation studies that demonstrate the overall accuracy and robustness of the design.

The thesis concludes with a summary of the major achievements and an evaluation, in the form of a comparison with existing systems.

# Acknowledgements

I would like to begin by thanking my supervisers: Prof. W. Bonath, University of Applied Sciences Gießen-Friedberg, Gießen, Prof. R. Comley, Middlesex University, London, Prof. K.T.V Grattan, City University, London for all their helpful advice and support throughout my period of study.

I would also like to thank Dr. Schultheiß (CEO) from Sensitec, for his valuable input to this work. I thank the University of Applied Sciences (Fachhochschule) Gießen-Friedberg for the use of the Laboratory of Microelectronic Design and other facilities. I also thank the BMBF of the German Goverment and Sensitec GmbH, my former employer, for their financial support, without which it would not have been possible for me to undertake this work.

Finally, I am deeply grateful to my parents Karl-Heinz and Roswitha and give special thanks to Eva-Maria for her constant companionship throughout this work.

# Contents

| 1 Introduction              |            |                 |                                |                                        | 1 |   |    |

|-----------------------------|------------|-----------------|--------------------------------|----------------------------------------|---|---|----|

| 1.1 Overall Sensor System   |            |                 |                                |                                        |   |   | 1  |

|                             | 1.2 Sensor |                 |                                |                                        |   | 2 |    |

|                             | 1.3        | 1.3 Electronics |                                |                                        |   |   | 2  |

|                             | 1.4        | Linear          | inearization and Interpolation |                                        |   |   | 4  |

|                             | 1.5        | Conce           | ptual For                      | mulation and Purpose                   |   | • | 6  |

| <b>2</b>                    | Low        | -Powe           | r and Lo                       | ow-Voltage Integrated Circuit Cells    |   |   | 7  |

| 2.1 Fundamental Limitations |            |                 |                                | mitations                              |   |   | 7  |

|                             |            | 2.1.1           | Large Si                       | gnal MOSFET Model                      |   |   | 7  |

|                             |            | 2.1.2           | Small Si                       | gnal MOSFET Model                      |   |   | 11 |

|                             |            | 2.1.3           | Minimu                         | m Supply Voltage Range                 |   |   | 13 |

|                             |            | 2.1.4           | Different                      | tial Input Stages                      |   |   | 14 |

|                             |            | 2.1.5           | Different                      | tial Rail-to-Rail Input Stages         |   |   | 15 |

|                             |            | 2.1.6           | Compon                         | ent Noise                              |   |   | 17 |

|                             | 2.2        | Analog          | gue Comp                       | parator                                |   |   | 21 |

| · ·                         |            |                 |                                | Comparator                             |   |   | 21 |

|                             |            | 2.2.2           | Advance                        | d Comparator                           |   |   | 24 |

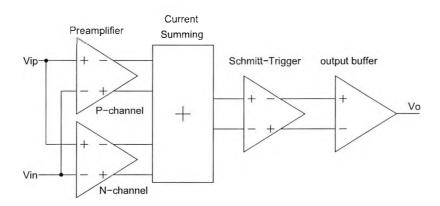

|                             |            |                 | 2.2.2.1                        | Comparator Principle                   |   | • | 24 |

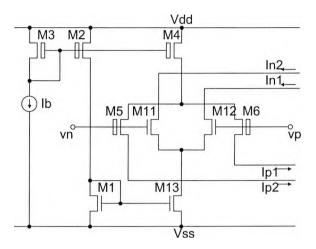

|                             |            |                 | 2.2.2.2                        | Preamplification and Summing Circuit . |   |   | 25 |

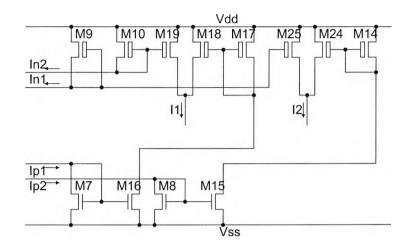

|                             |            |                 | 2.2.2.3                        | Schmitt-Trigger and Output Buffer      |   |   | 28 |

|                             |            |                 | 2.2.2.4                        | Rudimentary Comparator                 |   | • | 30 |

|                             |            |                 | 2.2.2.5                        | Comparator Optimization and Adaption   |   |   | 33 |

|                             | 2.3        | Differe         | ential Am                      | plifier                                |   |   | 43 |

|                             |            | 2.3.1           | Input St                       | age                                    |   |   | 43 |

|                             |            |                 | 2.3.1.1                        | Common Mode Input Range                |   |   | 43 |

|                             |            |                 | 2.3.1.2                        | Current Sources                        |   | • | 45 |

|                             |            |                 | 2.3.1.3                        | Differential Input Transistor Pair     |   |   | 46 |

|                             |            |                 | 2.3.1.4                        | Active Load                            |   |   | 47 |

|                             |            |                 | 2.3.1.5                        | Input Transconductance                 |   |   | 49 |

|                             |            | 2.3.2           | Output                         | Stage                                  |   |   | 50 |

|          |                 | 2.3.3  | Rudimentary OPAMP                                                                                                                               |

|----------|-----------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------|

|          |                 |        | 2.3.3.1 Physical Design                                                                                                                         |

|          |                 |        | 2.3.3.2 Measurement Results                                                                                                                     |

|          |                 | 2.3.4  | OPAMP Optmization and Adaption                                                                                                                  |

|          |                 |        | 2.3.4.1 Power Supply Independent Bias Current 59                                                                                                |

|          |                 |        | 2.3.4.2 Overall Topology                                                                                                                        |

|          |                 |        | 2.3.4.3 Performance Evaluation                                                                                                                  |

|          | 2.4             | Transı | mission Gate                                                                                                                                    |

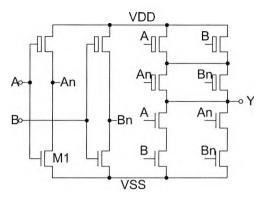

|          | 2.5             | Digita | l Cells                                                                                                                                         |

| 3        | Syst            | tem A  | rchitecture 79                                                                                                                                  |

|          | 3.1             | Sensor | Input Interface                                                                                                                                 |

|          |                 | 3.1.1  | Sensor Element and Gauge                                                                                                                        |

|          |                 | 3.1.2  | Sensor Noise                                                                                                                                    |

|          |                 | 3.1.3  | Signal Amplification                                                                                                                            |

|          | 3.2             | ~      | Conditioning Methodology                                                                                                                        |

|          |                 | 3.2.1  | Resolution and Resolution Enhancement                                                                                                           |

|          |                 | 3.2.2  | Folding A/D conversion concept                                                                                                                  |

|          |                 |        | 3.2.2.1 Dynamic Range of Flash Converters 86                                                                                                    |

|          |                 |        | 3.2.2.2 Dynamic Related Reference for Flash Con-                                                                                                |

|          |                 |        | verters                                                                                                                                         |

|          |                 |        | 3.2.2.3 Input Signal Folding                                                                                                                    |

|          |                 | 3.2.3  | Nonlinear Signal Conversion                                                                                                                     |

|          | 3.3             |        | nce Voltage Generation                                                                                                                          |

|          | 3.4             | Outpu  | t Interface                                                                                                                                     |

| 4        |                 | deling | 102                                                                                                                                             |

|          | 4.1             | •      | eto Resistive Sensor Model                                                                                                                      |

|          | 4.2             |        | Model for the System Architecture                                                                                                               |

|          |                 | 4.2.1  | Mismatch Error of the Resistor String 105                                                                                                       |

|          |                 | 4.2.2  | Iterative Overall Error Model                                                                                                                   |

|          |                 |        | 4.2.2.1 Basic Functionality $\dots \dots \dots$ |

|          |                 | 40.0   | 4.2.2.2 Folding Procedure                                                                                                                       |

|          |                 | 4.2.3  | Differential Error and Integral Nonlinearity                                                                                                    |

|          |                 | 4.2.4  | Position Error                                                                                                                                  |

| <b>5</b> | $\mathbf{Syst}$ | tem Ev | valuation 119                                                                                                                                   |

|          | 5.1             | Exper  | imental Results of Signal Conditioning Unit 119                                                                                                 |

|          | 5.2             | System | n Simulation Results                                                                                                                            |

|          |                 | 5.2.1  | System Architecture                                                                                                                             |

|          |                 | 5.2.2  | Benchmark Results                                                                                                                               |

|          |                 |        |                                                                                                                                                 |

|   | 5.3 | Discus | sion                  | 128 |

|---|-----|--------|-----------------------|-----|

|   |     | 5.3.1  | Chain of Evidence     | 128 |

|   |     | 5.3.2  | Component Level       | 129 |

|   |     | 5.3.3  | System Level          | 131 |

|   |     | 5.3.4  | Implementation        | 133 |

|   |     | 5.3.5  | Optimisation Prospect | 134 |

|   |     | 5.3.6  | Classification        | 135 |

| 6 | Con | clusio | n                     | 137 |

# List of Symbols

| Symbol              | Description                                                  | Unit                |

|---------------------|--------------------------------------------------------------|---------------------|

| α                   | transistor dimension ratio for hysteresis voltage            | 1                   |

| $\alpha_{R0}$       | temperature coefficient of $R_0$                             | Κ                   |

| $\alpha_{\Delta R}$ | temperature coefficient of the hub of the resistance         | Κ                   |

| $\alpha_{off}$      | power supply dependent temperature coefficient of the offset | Κ                   |

| $\beta$             | transconductance coefficient                                 | $A/V^2$             |

| $\beta_f$           | feedback factor                                              | 1                   |

| $\gamma$            | body effect parameter                                        | sqrtV               |

| $\lambda$           | channel length modulation                                    | 1/V                 |

| $\mu$               | charge carrier mobility                                      | $cm^2/Vs$           |

| $\omega_t$          | unity gain frequency                                         | 1/s                 |

| $\phi_F$            | Fermi potential                                              | V                   |

| $\varphi$           | phase angle of the sensor element signals                    | rad                 |

| $\varphi_k$         | ideal discrete phase angle                                   | rad                 |

| $\psi_{min}$        | minimum resolution                                           | m                   |

| $d_{off}$           | power supply dependent offset                                | A / V               |

| $g_m$               | transconductance                                             | A / V               |

| $g_d$               | drain conductance                                            | A / V               |

| $g_{mw}$            | transconductance weak inversion                              | A / V               |

| $g_{mm}$            | transconductance moderate inversion                          | A/V                 |

| $g_{dw}$            | drain conductance weak inversion                             | A / V               |

| $g_{dm}$            | drain conductance moderate inversion                         | A / V               |

| $i_{dwn}$           | white noise drain current                                    | А                   |

| $i_{dwn,w}$         | white noise drain current in weak inversion                  | А                   |

| n $($               | weak inversion slope factor                                  | 1                   |

| q                   | electron charge                                              | С                   |

| $r_{off}$           | offset equivalent resistance                                 | $\Omega$            |

| u                   | inversion coefficient                                        | 1                   |

| $v_n$               | noise voltage                                                | V                   |

| $v_{dwn}$           | white noise gate voltage                                     | V                   |

| $v_{dwn,w}$         | white noise gate voltage in weak inversion                   | V                   |

| $v_{fn}$            | flicker noise voltage                                        | V                   |

| $A_0$               | open loop amplification                                      | dB                  |

| $A_c$               | amplitude of the cosine                                      | V                   |

| $A_f$               | differential voltage amplification with feedback             | dB                  |

| $A_s$               | amplitude of the sine                                        | V                   |

| $A_v$               | differential voltage amplification                           | dB                  |

| $B_2$               | Early voltage parameter                                      | $V \cdot \sqrt{cm}$ |

# List of Symbols

| Symbol                        | Description                                     | Unit                  |

|-------------------------------|-------------------------------------------------|-----------------------|

| $C'_{ox}$                     | gate oxide capacitance                          | $F/m^2$               |

| $C_{ox}$                      | normalized oxide capacitance                    | $F/m^2$               |

| DNL                           | differential nonlinearity                       | 1                     |

| DR                            | dynamic range                                   | dB                    |

| $H_0$                         | intrinsic characteristic magnetic field         | A/m                   |

| $H_x$                         | extrinsic magnetic field in x-direction         | A/m                   |

| $H_y$                         | extrinsic magnetic field in y-direction         | A/m                   |

| INL                           | integral nonlinearity                           | 1                     |

| $I_{bias}$                    | bias current                                    | А                     |

| $I_d$                         | drain current                                   | А                     |

| $I_{ds}^{u}$                  | drain-source current                            | А                     |

| $I_S$                         | specific current, upper limit in weak inversion | А                     |

| $I_Z$                         | geometry dependent specific current             | А                     |

| $L^{2}$                       | channel length                                  | m                     |

| $N_A$                         | acceptor concentration                          | m                     |

| P                             | period                                          | m, t, rad, $^{\circ}$ |

| $\frac{1}{P_t}$               | position corresponding voltage                  | m, t, rad, $^{\circ}$ |

| Q                             | minimum sensor resolution                       | m, v, rud, m          |

| $\Delta R$                    | maximum change of the magneto resistance        | $\Omega$              |

| $R_0$                         | magneto resistance without magnetic field       | $\Omega$              |

| $R_{25^{\circ}}$              | magneto resistance at room temperature          | $\Omega$              |

| $R_{25^{\circ}}$<br>$R_{tot}$ | total resistance of the resistor chain          | $\Omega$              |

| $\frac{R_{tot}}{SNR}$         |                                                 | dB                    |

|                               | signal to noise ratio<br>slew rate              | UD<br>V/s             |

| $S_r$                         |                                                 | v/s<br>V              |

| $V_A$                         | Early voltage                                   | V<br>V                |

| $V_{bs}$                      | bulk-source voltage                             | V<br>V                |

| $V_{ds}$                      | drain-source voltage                            | V<br>V                |

| $V_{dsat}$                    | drain-source saturation voltage                 | V<br>V                |

| $V_{eff}$                     | effective gate-source voltage                   |                       |

| $V_{gs}$                      | gate-source voltage                             | V                     |

| $V_{gs,n}$                    | gate-source voltage n-channel transistor        | V                     |

| $V_{gs,p}$                    | gate-source voltage p-channel transistor        | V                     |

| $V_{hys}$                     | hysteresis voltage                              | V                     |

| $V_{in,cm}$                   | common mode input voltage                       | V                     |

| $V_n$                         | rms noise voltage                               | V                     |

| $V_{ref}$                     | reference voltage                               | V                     |

| I/                            | threshold voltage                               | V                     |

| $V_{th} \ V_{off}$            | uneshold voltage                                | ,<br>V                |

# List of Symbols

| Symbol       | Description                             | Unit |

|--------------|-----------------------------------------|------|

| $V_x$        | tap voltage of resistor ladder          | V    |

| $V_{x_i}$    | discrete tap voltage of resistor ladder | V    |

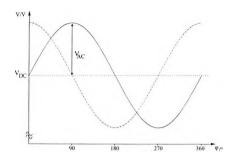

| $V_{ACs}$    | voltage amplitude of the sensor         | V    |

| $V_{DCs}$    | dc voltage level of the sensor          | V    |

| $V_{DD}$     | power supply voltage                    | V    |

| $V_{DD,min}$ | minimum power supply voltage            | V    |

| $V_{SS}$     | negative power supply voltage           | V    |

| $V_T$        | thermal voltage                         | V    |

| $\hat{W}$    | channel width                           | m    |

## List of constants

| Symbol             | Description                    | Value                    | Unit                                |

|--------------------|--------------------------------|--------------------------|-------------------------------------|

| $\varepsilon_{ox}$ | permitivity of silicon dioxide | $3.45 \cdot 10^{-13}$    | $\overline{\mathrm{F}}/\mathrm{cm}$ |

| $\varepsilon_{si}$ | permitivity of silicon         | $1.04 \cdot 10^{-12}$    | F/cm                                |

| k                  | Boltzmann Constant             | $1.387 \cdot 10^{-23}$   | $\frac{V \cdot C}{K}$               |

| q                  | magnitude of electron charge   | $1.602 \cdot 10^{-19}$   | С                                   |

| $\mu_{m0}$         | magnetic field constant        | $1.256637 \cdot 10^{-6}$ | $\frac{V \cdot s}{A \cdot m}$       |

# Chapter 1

# Introduction

## 1.1 Overall Sensor System

In many of today's appliances and applications it is useful or necessary to determine the positions like length and angle, for instance in brake systems of a car or in industrial sawing machines. Hence a market has grown with a broad variety of functionality and features. Some things have become established such as interfaces at the input and output, methods for resolution enhancement or typical supply voltages.

Various types of physical effects are used for position measurement like optical, capacitive, inductive or magnetic sensor phenomenons. Magneto resistive sensors are based on the anisotropic magneto resistive effect and are well suited for this measurement task, because they are able to work in harsh environments compared with other sensor principles like optical [1] or capacitive position sensors. One further advantage is that they can be produced as integrated devices with lithographic processes in very high volumes at low chip prices.

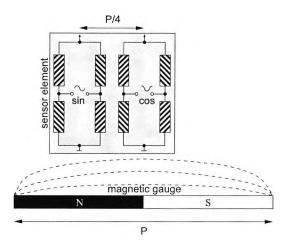

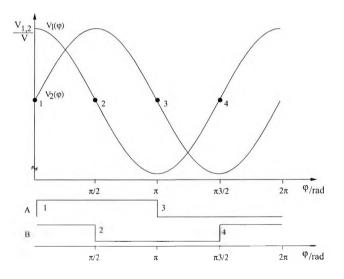

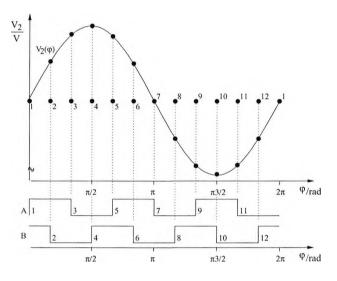

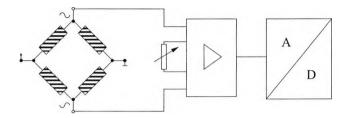

Anisotropic Magneto Resistive (AMR) sensor elements exhibit changes of resistance within external moving magnetic fields. The phenomenon effect is a change of the conductivity of the material (Permalloy) as a function of an extrinsic magnetic field. Typically, the resistors are arranged in Wheatstone bridges, in order to provide differential signals with common mode rejection. At the output they provide a signal, which is comparable to other measurement systems for instance laser tracking systems [2] or optical encoders which generate quadrature sinusoidal signals by optical slits [3]. Some of these sensors generate two sine waveforms which normally show a phase shift of 90°. Based on these two signals, different signal processing methods have been developed. Essentially two properties of these signals are used. First, the phase shift between both signals indicates a direction, because the shift can be either plus or minus 90°. Second, some mathematical procedures have been established for linearization and interpolation [4]. Those algorithms can be implemented in software, based in arithmetic logic units, or hardware based in digital or analogue signal processing units. With these methods the resolution of such measurement systems can be increased.

This work contributes to an advance in position measurement systems. It focuses on one main topic: "Reduction of the total power consumption"

All of the known systems work within a conventional supply voltage range of 3 V to 5 V, but they are not optimised with respect to the power consumption. In order to minimise power consumption the supply voltage has to drop. This is also a requirement for future technologies for integrated circuits. Due to reliability aspects, the supply voltage has also to be reduced for newer technologies with reduced geometries of electronic elements [5]. Wake up systems or non-continuous time systems can be used to reduce consumption but they do not solve the basic problem that the supply voltage must drop. The focus of this work is an optimised signal processing circuit that operates at a minimised supply voltage. Basically the circuit should be driven at the lowest possible voltage supplies while maintaining an appropriate level of performance. Fundamental margins are given for the minimum voltages to drive MOS transistors and CMOS circuits.

### 1.2 Sensor

Magneto resistive sensors are also able to work at low voltages. The minimum possible supply voltage is limited by the signal to noise ratio [6]. By reducing the supply voltage the power consumption of the sensor also decreases. Therefore the magneto resistive sensor is well suited for position measurement at low-voltages and low-power due to available high impedance sensor bridges. This type of sensor does not limit the system requirements. All borders are given by the electronics and require new architectures to find the margins of operation.

## **1.3** Electronics

In order to reach the aim of the thesis the problem was divided into two parts. First, the component level influences significantly the power consumption. Second, special architectures at system level can contribute to an advance in saving power consumption.

The purpose on component level is to develop basic cells for integrated circuits. Necessarily, special integrated circuit components have to be developed because such components as needed are not available for this sensor application. Researchers invested considerable effort to develop low-voltage analogue cells in order to facilitate the decrease of the power supply voltages down to usual power supply voltages for digital circuits. On the one hand, layouts and element dimensions of these developed analogue cells are not compatible for different processes but on the other hand methods and topologies can be transferred to other technologies. Due to that a lot of solutions for low-voltage and low-power operation are valid for other CMOS technologies.

At the element or transistor level, the lowest operating voltages and lowest operating currents are reached, if the transistor is driven in the weak inversion or sub-threshold region. Circuit developments based on this operating region of transistors allow operating voltages down to the lowest fundamental limits. Traditionally, circuit designers set the margins for the transistor operating region to the lowest possible value in the strong inversion region.

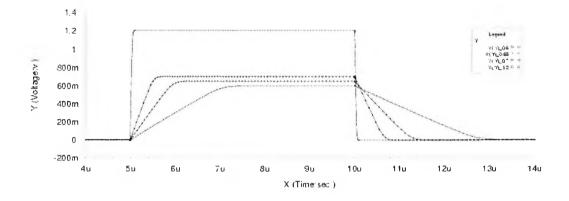

One major shortcoming occurs by driving the transistor in the sub-threshold region, where the MOS transistors behave similarly to bipolar transistors. This insufficiency is serious. Due to the drastic current reduction the frequency bandwidth is significantly decreased. Nevertheless components such as OPAMPs must be developed which are sufficient for the frequency requirements of the system. If, for instance, the position measurement system needs a 3dB frequency of about 10 kHz and a gain of 30, then a gain bandwidth product of 300 kHz would be sufficient. This is a typical value for many applications. Hence application specific developments with reduced power supply voltages and bias currents must advance this position measurement system.

Some techniques are proposed to enhance gain and bandwidth in weak inversion operation up to 5 times [7]. But in order to save as much power consumption as possible the circuit topologies should be kept as simple as possible. Any additional circuit element needs to be driven and consumes power. An improvement in gain and bandwidth is only advisable if it is required.

Basically, analogue circuits operate with operational amplifiers and comparators. Therefore the focus is set on these components. The dynamic range for such components is reduced if the power supply voltage decreases. Hence, it becomes more important to get rid of limitations that are governed by the component architecture. For instance, the differential amplifier should have a rail-to-rail input and output characteristic. This influences also the smallest possible supply voltage. The problem is to find architectures that enlarge the power supply voltage requirement by only a small amount.

One further problem refers to the threshold voltage. In contrast to the reduction of the power supply voltages for newer technologies, the threshold voltage decreases only slightly [5]. As a result, the ratio of the supply voltage to the threshold voltage decreases and analogue signal processing suffers due to the loss of headroom. This means that the threshold voltage determines significantly the minimum possible power supply voltage.

## 1.4 Linearization and Interpolation

On the system level, two fundamental requirements exist. First, at the input, nonlinear signals drive the electronic circuit, whereas at the output linear signals are expected. The circuit has therefore to provide a method of linearization. Second, the resolution of the position sensor must be improved by electronic signal processing in order to bypass the limited resolution that is given by the sensing element.

Existing methods linearize the signal with digital [2], [3], [8], [9] as well as analogue techniques [10, 11] but these methods are neither developed for low voltage operation nor optimised accordingly for low power consumption and are not suitable for battery applications with long battery lifetime.

Furthermore, digital linearized and interpolated signals consume substantial power if they work with a high clock frequency. This means considerable power consumption. Hence the digital computation must be reduced or prevented. An important issue here is how many digital computations are necessary? Could the same task be done by an analogue circuit with less power consumption?

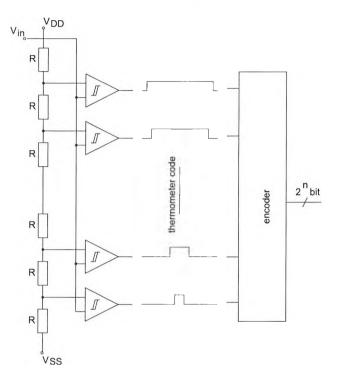

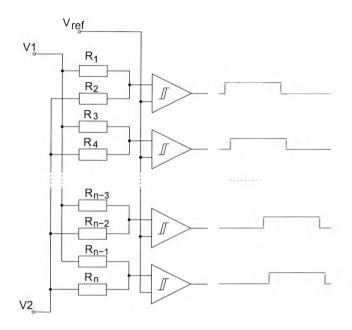

Methods that linearize and interpolate the signal in an analogue way, use a large number of components like OPAMPs and comparators. For instance, if an ADC with a flash topology is to be operated over the complete supply voltage range, then a lot of comparators are required for high resolutions and the analogue input signal should have large amplitudes in order to minimise the quantization error. Therefore, an amplitude independent method is needed as proposed by [12]. This method suffers, however, from high power consumption, as a large number of redundant components is required in order to convert an analogue input signal that provides an intrinsic symmetry.

A further objective of this thesis is, therefore, to find an improved topology that reduces the power consumption and also works at the minimum limits of the supply voltage range. Two very important requirements for position measurement systems are the position resolution and the accuracy. The accuracy of a sensor system is not entirely predictable, because offset, mismatch and parameter scatter of elements and components cannot be easily determined, but the accuracy can be estimated by worst case assumptions of components. That means also the accuracy is strongly influenced by the topology and layout of the components. One task is therefore to develop layouts which minimise the accuracy problem and give careful consideration of the component arrangement, which influence the accuracy. For example, resistors must be matched, the higher the number of resistors that are related together the higher the overall error. The dimensions of the resistors must be a compromise of accuracy and chip area. An error model which takes all errors into account must be developed to estimate the overall error and to determine the main influences. Furthermore, with such a model the influence of the matching is valuable.

Concerning the resolution, the position sensing system should have a resolution that is much higher than the resolution that is given by the sensor. There is a direct relationship between the resolution and the quantization of the A/D Converter. Hence, a topology must be found that operates on the one hand at low supply voltages and that saves energy by saving components and on the other hand allows a high resolution by maintaining or improving the dynamic range. The method should take into consideration that the achievable resolution is in correlation to the required precision. A scalable resolution would deal with either high resolution with less accuracy or with low resolution with an advanced accuracy. One key task is to find and evaluate a topology for resolution enhancement.

## 1.5 Conceptual Formulation and Purpose

This work covers four main topics.

First, the development of basic analogue cells which is presented in chapter 2. These cells are the fundamental integrated circuit cells that are used for the work on the system level.

Second, the system level is presented in chapter 3 and includes a special methodology for signal conditioning, particularly a new A/D conversion concept and signal linearization, respectively.

Third, models for the sensor and the system architecture are presented in chapter 4. This includes investigations on the system accuracy.

Fourth, in chapter 5 the measurement and simulation results are presented. This chapter ends with a discussion of the simulation and measurement results.

# Chapter 2

# Low-Power and Low-Voltage Integrated Circuit Cells

### 2.1 Fundamental Limitations

### 2.1.1 Large Signal MOSFET Model

#### Strong Inversion

The operating range of MOS transistors can be separated into two regions [16], the triode (or linear) and the saturation (or active) region, each of which is described by special model equations. Within the so-called triode region the transistor is not saturated and the drain current  $I_d$  can be written by the following expression 2.1.

$$I_d = \mu \cdot C_{ox} \cdot \frac{W}{L} \cdot \left[ (V_{gs} - V_{th}) \cdot V_{ds} - \frac{1}{2} V_{ds}^2 \right]$$

(2.1)

for

$$V_{gs} \ge V_{th}$$

and  $V_{ds} < V_{dsat} = V_{gs} - V_{th} = V_{eff}$  (2.2)

Equation 2.1 contains the fixed parameters channel width W, channel length L, the oxide capacitance per unit area  $C_{ox}$  and the technology dependent mobility  $\mu$  (for NMOS  $\mu_n$ , for PMOS  $\mu_p$ ). In this domain, the transistor is driven with the gate-source voltage  $V_{gs}$  and the drain-source voltage  $V_{ds}$ . The threshold voltage  $V_{th}$  can generally be assumed to be constant, particularly if no body effect occurs.

If  $V_{ds}$  leaves the range of definition 2.2, the transistor is saturated. In this range the drain current is specified by equation 2.3.

$$I_d = \frac{1}{2} \cdot \mu \cdot C_{ox} \cdot \frac{W}{L} \cdot \left(V_{gs} - V_{th}\right)^2 \left(1 + \lambda \cdot V_{ds}\right)$$

(2.3)

for

$$V_{gs} \ge V_{th}$$

and  $V_{ds} \ge V_{dsat} = V_{gs} - V_{th} = V_{eff}$  (2.4)

The channel length modulation  $\lambda$  in equation 2.3 is often small and may be ignored. Hence,  $\lambda \cdot V_{ds} = 0$  is assumed and equation 2.3 becomes independent of the drain-source voltage.

In low-voltage and low-power circuit design the meaning of strong inversion operation of MOS devices is high. Such circuits operate at the margins of the operating range, which are determined by the definition 2.4, by maintaining the typical performance of integrated circuits that typically operate at higher power supply voltages and bias currents. From the performance viewpoint, like signal processing speed and noise considerations, strong inversion operation is the best choice.

In contrast, the strong inversion operation is not prefered if system requirements enforce lower power supply voltages and lower power consumption. In this case the devices can be driven below the threshold of the devices.

#### Weak Inversion

From the definition 2.2 and 2.4 it is given that when  $V_{gs} \ge V_{th}$  the transistor is driven in the strong inversion region. This is the classical operation region for circuit development. If  $V_{gs} < V_{th}$  then the operation region changes into the weak inversion (or subthreshold) region and the drain current becomes very small. Circuit developments with radically reduced current consumption work with very small currents below the threshold voltage e.g. battery supply applications. The behaviour of MOSFETs driven in this operating domain is similar to a bipolar transistor. Expression 2.5 describes the drain current in the subthreshold operating domain - the weak inversion domain - of MOS transistors.

$$I_d = I_S \cdot \frac{W}{L} \cdot e^{\frac{V_{gs} - V_{th}}{n \cdot V_T}} \cdot \left(1 - e^{-\frac{V_{ds}}{V_T}}\right) \cdot e^{-V_{bs} \cdot \left(\frac{1}{n \cdot V_T} - \frac{1}{V_T}\right)}$$

(2.5)

In equation 2.5 the thermal voltage  $V_T$  is calculated by  $V_T = \frac{k \cdot T}{q}$  with Boltzmann's constant  $k = 1.387e - 23 \ VC/^{\circ}$ K, the electronic charge  $q = 1.6e - 19 \ C$  and the temperature T. At room temperature  $V_T \cong 26 \ mV$ . Depending on the technology the slope factor n is typically in the range of 1 to 2. Also the *specific current*  $I_S$  is a technology constant and describes the current performance of the current in the weak inversion domain.  $I_S$  is calculated as follows (Eq. 2.6):

$$I_S = 2 \cdot n \cdot \mu \cdot C_{ox} \cdot V_T^2 \tag{2.6}$$

It is almost always valid to neglect the influences of  $V_{ds}$  and  $V_{bs}$  in equation 2.5 for hand calculation.  $V_{bs}$  is set to zero, if the body effect can be prevented and if  $V_{ds} > 4 \cdot V_T$  then the drain-source voltage is also negligible. The influence of  $V_{ds}$  is then smaller than 2%. Equation 2.5 can then be simplified as expressed in equation 2.7.

$$I_d = I_s \cdot \frac{W}{L} \cdot e^{\frac{V_{gs} - V_{th}}{n V_T}} = I_Z \cdot e^{\frac{V_{gs} - V_{th}}{n \cdot V_T}}$$

(2.7)

$$for \quad V_{ds} > 4 \cdot V_T \tag{2.8}$$

The transistor model of equation 2.7 is assumed to be saturated due to the fact that the drain current is independent of the drain source voltage. Therefore the saturation condition 2.8 must be fulfilled. Sometimes designers set the saturation margin to  $6 \cdot V_T$  or higher in order to reach more robustness and reliability. For evaluation of minimum supply voltages the margin is taken at the lowest value of condition 2.8.

Weak inversion operation of MOS devices has become popular since lowpower and low-voltage applications are required. Often only parts of a circuit are biased with very low currents and below the threshold of the devices. The correlation between  $I_d$  and  $V_{gs}$  can be used to lower  $V_{gs}$  in order to reduce the power supply voltage range which is mainly determined by  $V_{gs}$ . For low-voltage design low technology dependent  $V_{th}$  of n-channel and p-channel devices are desired.

But due to the resulting low currents in weak inversion operation the signal processing speed is drastically decreased and also the noise level rises (sec. 2.1.6). A trade-off between strong and weak inversion operation might be the moderate inversion region.

#### **Moderate Inversion**

The transition between the strong and the weak inversion operation of a transistor is smooth and the so-called moderate inversion region. This region is defined by (Eq. 2.9):

$$\frac{1}{10}I_d < I_Z < 10I_d \tag{2.9}$$

No explicit model is available for only this intermediate region. As reported in [17] many problems can occur in simulation regarding the simulation accuracy. Several semi empirical expressions have been developed, for example [18]. Another approach is proposed in [19] which is dedicated to the design and analysis of low-voltage and low-current analogue circuits. With this model a balanced compromise between accuracy and simplicity is achieved. This model covers all regions of operation from strong inversion to weak inversion inclusive of moderate inversion and in addition saturation and non-saturation. This model is normally known as the bulk referred model [17], but if it is extended a source referenced model can be written as

$$I_{ds} = 2n\mu C_{ox} V_T^2 \frac{W}{L} \left\{ \left[ \ln^2 (1 + e^{\frac{V_{gs} - V_{th}}{2nV_T}}) \right] - \left[ \ln^2 (1 + e^{\frac{V_{gs} - V_{th} - nV_{ds}}{2nV_T}}) \right] \right\}$$

(2.10)

Equation 2.10 can be simplified for transistors in saturation. Then the second term becomes negligible. Thus the equation can be expressed by

$$I_{ds} = 2n\mu C_{ox} V_T^2 \frac{W}{L} \left[ \ln^2 (1 + e^{\frac{V_{gs} - V_{th}}{2nV_T}}) \right] = I_Z \left[ \ln^2 (1 + e^{\frac{V_{gs} - V_{th}}{2nV_T}}) \right]$$

(2.11)

The model equation 2.11 is valid in all regions of inversion if the transistor is saturated. The slope factor n is given by

$$n = 1 + \frac{\gamma}{2\sqrt{V_{sb} + \phi_F}} \tag{2.12}$$

where  $V_{sb}$  is the source-bulk voltage.  $\phi_F$ , the Fermi potential, can be written as

$$|\phi_F| \approx |V_T \ln \frac{N_A}{n_i}| \tag{2.13}$$

with  $N_A$  the acceptor concentration and  $n_i$  the intrinsic carrier concentration. Depending on the doping concentration the Fermi potential is at room temperature between 0.23 and 0.47. A good approximation is therefore 0.35.

The parameter  $\gamma$  in equation 2.12 for the slope factor is as follows:

$$\gamma \equiv \frac{\sqrt{2q\epsilon_{si}N_A}}{C_{ox}} \tag{2.14}$$

where q is the electron charge,  $\epsilon_{si}$  is the permittivity of silicon,  $N_A$  the acceptor concentration and  $C_{ox}$  the gate capacitance per unit area. Typical values for  $\gamma$  are in a range of 0.2 and 2.0. If for example  $\gamma=0.8$  and  $\phi_F=0.35$  and no body effect is present and therefore  $V_{sb}=0$ , the slope factor n is  $\approx$  1.7, which can be taken for rough estimations.

Regarding the performance, moderate inversion operation is a good compromise if power consumption and the power supply voltage should be reduced. The model behaviour around the threshold voltage of the device is less accurate than other models in respect of hand calculations. Nonetheless this large signal model provides the opportunity for circuit calculations for devices that are neither operated in strong nor in weak inversion. The meaning of driving circuits or parts of a circuit in moderate inversion has become more usual. Also in this work the moderate inversion region is often used for circuit parts.

The large signal models are used for determination of drain current as well as for calculations of  $V_{gs}$ . Particularly the determination of  $V_{gs}$  is important in order to define the mode of operation.

### 2.1.2 Small Signal MOSFET Model

#### Strong Inversion

When using the small signal analysis model of MOSFET transistors, it is important to take the operating point into account. This was briefly discussed in chapter 2.1.1, where the operating point is adjusted with the drain current. The derivation of equation 2.3 with respect to the gate-source voltage gives the transistor transconductance  $g_m$  as expressed in equation 2.15.

$$g_m = \frac{\partial I_d}{\partial V_{gs}} = \sqrt{2\beta I_d} \tag{2.15}$$

If equation 2.3 is derived with respect to the output or drain-source voltage, then the result is the output conductance of the transistor (Eq. 2.16).

$$g_d = \frac{\partial I_d}{\partial V_{ds}} \approx \lambda \cdot I_d \tag{2.16}$$

### Weak Inversion

For the weak inversion region, the model for the drain current is given by equation 2.5. As discussed above, the derivations with respect to the gate-source voltage and the drain-source voltage give the small signal parameters (Eq. 2.17, 2.18).

$$g_{mw} = \frac{\partial I_{dw}}{\partial V_{gs}} = \frac{I_d}{n \cdot V_T} \tag{2.17}$$

$$g_{dw} = \frac{\partial I_{dw}}{\partial V_{ds}} = \frac{1}{e^{\frac{V_{ds}}{V_T}} - 1} \cdot \frac{I_d}{V_T}$$

(2.18)

The derivation of the drain current with respect to the drain source voltage is beset with a problem. If  $V_{ds}$  becomes very large, which indeed is a typical case, then  $g_{dw}$  converges against zero or  $r_{dw}$  becomes infinite, respectively. This is very inaccurate and not useful. The model for  $g_d$  is better expressed by the equation 2.23 from the all region model which is particularly true for moderate inversion.

Conspicuous in both equations 2.17 and 2.18 is that both the transconductance  $g_{mw}$  and the output conductance  $g_{dw}$  depend on  $V_T$  and hence on the temperature. This implies for the circuit development, that only in the case of relations where  $V_T$  is cut a compensation of the temperature is partially or completely possible. This particularly influences the poles and zeros of the frequency response. As a consequence the 3dB frequency is shifted over temperature and makes the compensation of amplifiers difficult.

#### **Moderate Inversion**

The small signal model in moderate inversion is similar to the weak inversion model. The calculation is based on the inversion coefficient u which is defined by

$$u = \frac{I_d}{I_Z} \tag{2.19}$$

With equation 2.19 a special function can be expressed which is used in several further equations.

$$f(u) = \frac{1}{2}(\sqrt{1+4u}+1)$$

(2.20)

This equation is used in the expression for the transconductance which is given by

$$g_{mm} = \frac{I_d}{nV_T} \frac{1}{f(u)} \tag{2.21}$$

The conductance for transistors in moderate inversion is based on the Early voltage as for bipolar transistors. The Early voltage is given by

$$V_A = B_2 \cdot L \cdot \sqrt{N_A} \tag{2.22}$$

where  $N_A$  is the acceptor concentration, L is the gate length and  $B_2$  is a parameter which is in a range of  $1 \cdot 10^{-3}$  to  $2 \cdot 10^{-3} V \cdot \sqrt{cm}$ . In conjunction with equation 2.22 the conductance is

$$g_{dm} = \frac{I_d}{V_A} \tag{2.23}$$

The transconductance is employed in several equations for circuit calculation. The right small signal model should be applied for hand calculation in order to achieve the highest accuracy compared with the simulation and measurement results.

### 2.1.3 Minimum Supply Voltage Range

Analogue circuits which operate with significantly reduced supply voltages may work at the fundamental margins of the elements. As described in chapter 2.1.1 one of the limiting parameters for saturated transistors is the minimum drain-source  $V_{ds}$  voltage. The voltage must be larger than  $4V_T \approx$ 100mV. This is much less than for transistors working in the strong inversion domain. For calculations of the minimum supply voltage margins of CMOS circuits, the number of stacked transistors between the supply voltages is vital. The smaller the number of transistors the smaller the minimum supply voltage may shrink. But it is not only  $V_{ds}$  that determines the supply voltage range.  $V_{gs}$  has the most important significance for the calculation of the minimum possible supply voltage. Both,  $V_{gs}$  and  $V_{ds}$  determine the minimum power supply voltage, which can be expressed for a single simple gain stage by equation 2.24.

$$V_{DD,min} = V_{gs} + V_{ds} = V_{th} + V_{eff} + 4V_T$$

(2.24)

For circuit developments using the strong inversion region  $V_{qs}$  is larger than  $V_{th}$ . If the circuit is driven in the weak inversion region  $V_{gs}$  can be chosen smaller (below  $V_{th}$ ). Therefore, with respect to the minimum possible power supply it is an advantage to drive analogue circuits in the weak inversion region. The minimum possible power supply voltage can only be achieved for very simple topologies like single stage amplifiers, because only one gatesource voltage and one drain-source voltage limit the number of components. For example, if the threshold voltage is 0.6 V the minimum resulting strong inversion supply voltage is  $V_{DD,min,si} = V_{gs} + V_{ds} = 0.6V + 0.2V + 0.4V = 1.2V$ and for weak inversion  $V_{DD,min,wi} = V_{gs} + V_{ds} = 0.6V - 0.1V + 0.1V = 0.6V$ . For more complex circuits, the minimum power supply voltage increases mostly by some further stacked saturation voltages. As a result the circuit topology should have less stacked or cascoded elements but more cascaded elements. In the following chapters it is described that most analogue circuits, such as OPAMPs, need higher supply voltages due to their more complex architectures.

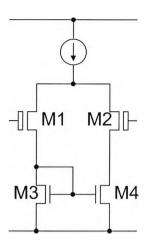

Figure 2.1: Simple differential amplifier with an active current mirror load

### 2.1.4 Differential Input Stages

Conventional differential input stages consist of a differential input transistor pair, a current source and a load, which is usually an active transistor in CMOS circuits. Depending on the type of input transistor pair, PMOS or NMOS, the common mode input range is limited to either the positive or to the negative power supply voltage range. Differential input stages which work with an active current mirror load are limited in respect of the common mode input range [31],[32].

Figure 2.1 shows an input stage of a conventional differential amplifier with an active current mirror load. In contrast to a resistive load, the voltage drop for an active load is at a minimum one gate-source voltage. This is caused by the diode-connected-transistor M3. The common mode input range is reduced, due to the shift of the drain potential to one gate-source voltage [33]. The common mode input range is therefore given by (Eq. 2.25)

$$V_{ss} + V_{gs,n} + V_{th,p} \le V_{in,cm} \le V_{DD} - V_{ds} - V_{sg,p}$$

(2.25)

where  $V_{gs,n}$  represents the gate-source voltage of the load transistor,  $V_{th,p}$  the threshold voltage of the PMOS input transistors,  $V_{ds}$  the drain-source voltage of the current source and  $V_{sg,p}$  the gate-source voltage of the input pair. M3 may push the drain potential of M1 out of saturation at low power supply voltages.

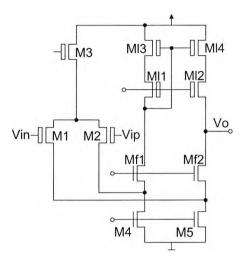

As a result, this problem must be avoided for low voltage operations. Instead of diode-connected-transistors, load transistors which operate with only one saturation voltage should be used. Such topologies have a significantly enlarged common mode range. For instance, cascode or folded cascode loads may be inserted. In the following Fig. 2.2 a folded cascode is depicted.

Figure 2.2: Differential amplifier with a folded cascode load

Both Fig. 2.1 and Fig. 2.2 have the same input stage and distinguish themselves only by the load. The advantage of the folded cascode topology is the improved common mode input range, which is given by

$$V_{ss} \le V_{in,cm} \le V_{DD} - V_{ds,p} - V_{gs,p}$$

(2.26)

As a result, the cascode load architecture is preferred in low voltage design. Furthermore input stages with cascode loads can realize a higher gain compared with the architecture of figure 2.1.

Nevertheless one common insufficiency exists for both input stages - the limited common mode input range. In order to overcome this problem, particularly in low-voltage design, complementary input stages must be inserted as described in the next chapter 2.1.5.

### 2.1.5 Differential Rail-to-Rail Input Stages

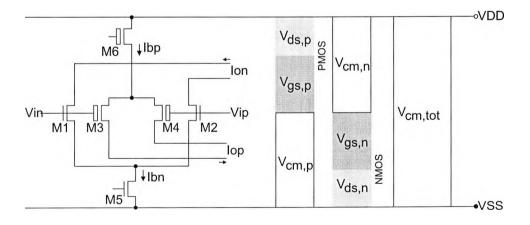

The previous section 2.1.4 described input stages which consist of a single transistor pair. Both NMOS and PMOS input stages are possible, depending on the system requirements. Such input stages suffer from an input common mode range that is limited by the gate-source voltage of the input transistors and the drain-source voltage of the tail current source (Eqn. 2.26). Furthermore, if the input voltage is kept close to  $V_{SS}$  (or in case of a NMOS)

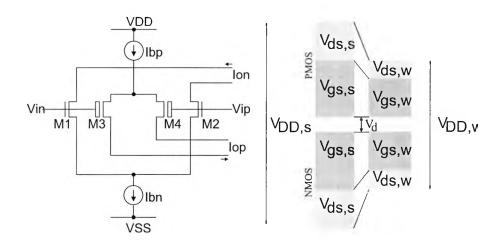

Figure 2.3: Rail-to-rail input stage

differential pair close to  $V_{DD}$ ) with a very small headroom, the power supply voltage can be as small as possible without the property of a signal processing reaching from the negative to the positive supply voltage at the input.

In oder to overcome this limit a PMOS and a NMOS differential input stage must be put in parallel. Then the signal processing is possible over the complete common mode input voltage range reaching from the negative to the positive supply rail. Figure 2.3 shows this architecture.

Concerning the requirement of a minimum power supply, rail-to-rail input stages need the double supply voltage compared with a single one. This is indeed a drawback, but in most applications of OPAMPs in low-voltage environments rail-to-rail input stages are necessary due to the fact that the operation points at the amplifier input are mostly at  $V_{DD}/2$ . This is not feasible with single input stages that operate at their minimum possible power supply voltage.

The minimum power supply voltage for a rail-to-rail input stage is given by

$$V_{DD,min} = 2V_{qs} + 2V_{ds} (2.27)$$

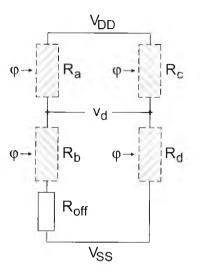

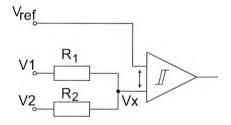

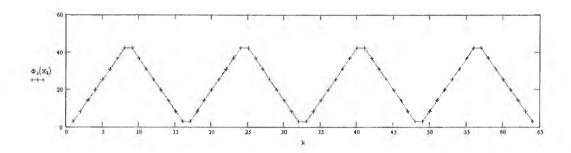

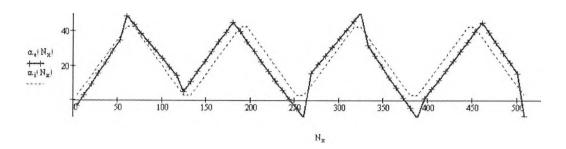

if  $V_{gs,n} = V_{gs,p}$  and  $V_{ds,n} = V_{ds,p}$ . Equation 2.27 is valid for all operation regimes. In order to satisfy these conditions the current sources have to conduct the same current. In addition, the unequal charge carrier mobilities of PMOS and NMOS transistors  $\mu_{0,p}$  and  $\mu_{0,n}$  should be equalized by the W/L ratios. In order to balance out the drain-source voltages of the current sources, the different charge carrier mobilities should be compensated and the gate-source voltages should be the equal. Figure 2.3 shows all voltages which determine the minimum power supply voltage. The minimum is reached if  $v_d$  is  $\approx 0$ . In traditional circuit design  $v_d$  is in a range of some volts. Each of the traditional circuits would also allow the power supply to be reduced down to  $v_d \approx 0$ . The smaller  $V_{th}$  the smaller  $V_{DD}$  can be. If the input stage is biased in the weak inversion domain the power supply voltage is further reducible because  $V_{gs}$  and  $V_{ds}$  shrink compared with a signal processing biased in the strong inversion region. This is indicated by the suffixes "s" and "w" of the voltages.

One drawback regarding the power consumption is that such input stages consume a double current because both input stages need to be biased separately. Moreover, the additional transistors enlarge the dimensions of the layout and the used chip area.

### 2.1.6 Component Noise

MOS transistors have so far been assumed to be only time dependend on terminal voltages, but this not exactly true. The following considerations refer to an inherent noise of MOS transistors and not to interference noise of the system or the environment. The sensor element correlated noise which occurs in addition is discussed in section 3.1.2. Inherent noise is a fundamental circuit property and cannot by eliminated but may be reduced if the resulting equations of this chapter are taken as design rules. The drain current exhibits current fluctuations - the so-called random noise - which can be an important item in circuit design even if the signal to noise ratio is reduced by smaller supply voltages that limit the signal magnitude. The signal-to-noise ratio SNR of a signal node in a circuit is defined as

$$SNR \equiv 10 \log \left[ \frac{signalpower}{noisepower} \right]$$

(2.28)

In the time domain the noise voltage  $v_n(t)$  is defined by its rms value as

$$V_n \equiv \sqrt{\frac{1}{T} \int_0^T v_n^2(t) dt}$$

(2.29)

If one or more further noise sources exist, they have to be added as voltage or current sources based on Kirchhoff's law. For two individual voltage noise sources the total voltage noise is given by

$$v_{n,tot}(t) = v_{n1}(t) + v_{n2}(t)$$

(2.30)

Equation 2.30 becomes particularly important with regard to the total noise at the interface between the sensor element and the electronic circuit,

where the noise sources have to be added. At the drain of a DC biased single MOS transistor the current can be expressed as

$$i_{ds}(t) = I_d + i_n(t)$$

(2.31)

where  $I_d$  represents the DC current and  $i_n(t)$  the noise current of the transistor. Two dominant noise sources exist in MOS transistors. One is called flicker noise and the other white noise.

#### White Noise in the Strong Inversion Region

The transistor channel between the source and the drain has a resistive property. As is known in simple resistors there is a noise component which depends on the resistance itself and the temperature. The same phenomena occurs in the channel of the transistor which can be derived from the white<sup>1</sup> noise from a resistor. In the triode region the resistance is the drain-source resistance of the transistor. If the transistor is in the active region the resistance is not homogeneous and therefore the resistance has to be integrated over the channel [16]. The resistance can be approximated as  $R \approx 3/2g_m$ . For simplification the noise is considered at  $V_{ds} = V_{qs} - V_{th}$  as

$$\overline{i_{dwn}^2} = 4kT\frac{2}{3}g_m \cdot \Delta f \tag{2.32}$$

$$= 4kT \left[\frac{2}{3}\frac{W}{L}\mu C_{ox}(V_{gs} - V_{th})\right] \cdot \Delta f \qquad (2.33)$$

The white noise drain current  $i_{dwn}$  in equation 2.33 depends on Boltzmann's constant k, the temperature T and the transconductance  $g_m$ . If  $g_m$  is substituted, the noise current can be expressed depending of  $V_{gs}$ .

Sometimes it is useful to transform the noise current into an equivalent input noise voltage<sup>2</sup>. Then the white voltage noise  $v_{gwn}$  is gate-referred given by

$$\overline{v_{gwn}^2} = 4kT\left(\frac{2}{3}\right) \cdot \frac{1}{g_m} \cdot \Delta f \tag{2.34}$$

Both  $i_{dwn}$  and  $v_{gwn}$  depend naturally on the temperature, but also on bias conditions and the element dimensions because of the transconductance  $g_m$ , which is given by equation 2.15.

<sup>&</sup>lt;sup>1</sup>White noise is often called thermal noise because the spectral density function depends on the temperature  $v_n^2(f) = 4kTR$ , where k is Boltzmann's constant, T the temperature and R the resistance

<sup>&</sup>lt;sup>2</sup>In the small signal model the drain current can be expressed as  $I_d = V_{gs} \cdot g_m$

#### White Noise in the Weak Inversion Region

White noise in the weak inversion region is not identical compared with the white noise in the strong inversion region [34]. Devices operating in saturation, which is achieved if  $V_{ds} \ge 4 \text{ to } 6 V_T$ , have a noise current of

$$\overline{i_{dwn,w}^2} = 2qI'_{ds}(1 + e^{-\frac{V_{ds}}{V_T}}) \cdot \Delta f$$

(2.35)

were q is the electron charge and  $I'_{ds}$  the drain current in the saturation. One result of equation 2.35 is that the term  $1+e^{-\frac{V_{ds}}{V_T}}$  is negligible in saturation because at the minimum of  $4V_T$  the influence of  $V_{ds}$  is only 2 percent.

In order to obtain a similar result to the strong inversion region, equation 2.35 can be expressed in terms of  $g_{mw}$ . Substituting  $I'_{ds}$  by equation 2.17 and the thermal voltage  $V_T$  by  $V_T = kT/q$  gives

$$\overline{i_{dwn.w}^2} = 2nkT \cdot \left(1 + e^{-\frac{V_{ds}}{V_T}}\right) \cdot g_{mw} \cdot \Delta f$$

(2.36)

$$= 2q \cdot I_s \cdot \frac{W}{L} \cdot e^{\frac{V_{gs} - V_{th}}{nV_T}} \cdot \left(1 + e^{-\frac{V_{ds}}{V_T}}\right) \cdot \Delta f \qquad (2.37)$$

The equivalent input noise voltage of equation 2.37 can be derived if  $I_d = g_{mw} \cdot v_{gs}$  is applied. This results in

$$\overline{v_{gwn,w}^2} = 2nkT \cdot \left(1 + e^{-\frac{V_{ds}}{V_T}}\right) \cdot \frac{1}{g_{mw}} \cdot \Delta f \tag{2.38}$$

If the gate-referred input noise voltage in strong inversion (Eqn. 2.34) is compared with the gate-referred input noise voltage in weak inversion (Eqn. 2.38) it can seen that the transconductance  $g_m$  has a significant influence, because the terms 4kT and 2nkT are nearly equal for values of n in between  $1 \leq n \leq 2$ . Typical values of n are 1.5 to 1.8. Hence these terms can be assumed equal. The terms  $(\frac{2}{3})$  and  $(1 + e^{-\frac{V_{ds}}{V_T}})$  are also in the same range. Taking the worst case for  $V_{ds} \approx 4V_T$  results in a value around 1. The inaccuracies of the first comparison and the second are mutually compensated. For an estimation, if the transconductance in strong inversion  $g_m$  is about 100 times larger than the transconductance in weak inversion  $g_{mw}$  it results in a  $\sqrt{100}$  higher gate-referred input voltage noise for devices operating in weak inversion.

As a consequence the SNR (Eqn. 2.28) is about -20dB worse for circuits biased in weak inversion. In addition, if the supply voltage decreases for instance from 5V to 1V the SNR is then decreased by -27dB.

In low-voltage/low-power design white noise therefore becomes an important issue. Techniques in order to meet noise requirements of a system are only given by careful handling of  $g_{mw}$ . It might be useful to drive the first amplifying stage at the interface between sensor element and the subsequent electronics in the moderate inversion region with large W/L ratios of the transistors, in order to find a compromise.

Devices which are switched off, have left the saturation region and equation 2.33 becomes invalid. The conductance G is in this case very small because the resistance R of a closed transistor is high. Noise can therefore be neglected for switched off devices.

#### Flicker Noise

Several studies relate to a type of noise that dominates at low frequencies. This kind of noise is called flicker noise or 1/f noise. As will be shown, the flicker noise is proportional to the inverse of the frequency. This is a relatively slow process and hence, this phenomena appears at low frequencies and introduces a further noise current at the drain of the transistor. Two dominant theories  $[35], [36]^3$  explain this phenomena. On the one hand they have different physical origins but on the other hand the resulting models are similar with respect to the design viewpoint. One theory [35] attributes flicker noise in MOS transistors to extra electron energy at the boundary between Si and  $SiO_2$ . The other theory is based on mobility fluctuations caused by carrier interactions with lattice fluctuations [37]. This work concentrates on the latter model that predicts an influence in the transition between the strong and the weak inversion region.

As previously discussed for the white noise, this noise current can also be transformed into a *gate-referred* noise voltage based on the correlation  $i_d = g_m \cdot v_{gs}$ . The resulting flicker noise voltage  $\overline{v_{fn}^2}^4$  is expressed by

$$\overline{v_{fn}^2} = \frac{K(V_{gs})}{C_{ax}} \cdot \frac{1}{W \cdot L} \cdot \frac{\Delta f}{f}$$

(2.39)

In this equation 2.39  $C_{ox}$  (gate capacitance per unit area) is a fixed parameter given by the technology and  $(W \cdot L)^{-1}$  is given by the design. As a consequence the noise level can be influenced by W times L in the development process. This does not completely meet the requirement of the white noise, where the white noise depends on the ratio of W and L. Therefore W should be chosen as large as possible and for L a reasonable compromise

$<sup>^{3}\</sup>mathrm{These}$  are only two exemplary citations for various publications related to this phenomena

<sup>&</sup>lt;sup>4</sup>In SPICE the model [40] [41] is given by  $\overline{i_{fn,ds}^2} = \frac{KF \cdot I_{ds}^{AF}}{C_{ox} \cdot L_{eff}^2} \frac{\Delta f}{f}$ , where KF is the flicker noise coefficient, AF the flicker noise exponent,  $C_{ox}$  the gate capacitance per unit area,  $L_{eff}$  the effective channel length, f the frequency and  $I_{ds}$  is the drain current

must be found. But flicker noise is larger than white noise and hence L should at least not be chosen small in order to balance out both types of noise. With this technique flicker noise is reduced and white noise increased. The quantity  $K(V_{gs})$  is bias-dependent as reported by [36]. In strong inversion  $K(V_{gs})$  increases in an approximately linear fashion with  $|V_{gs} - V_{th}|$  and in weak inversion  $K(V_{gs})$  increases as  $|V_{gs}|$  decreases. For simplicity's sake no distinction will be made between NMOS and PMOS transistors in this work, where NMOS transistors are rather independent of  $|V_{gs}|$ . As a result the  $|V_{gs}|$  for low-voltage and low-power design should be chosen as close as possible to the threshold voltage in order to reduce the flicker noise.

The noise itself becomes worse the smaller the frequency and can be neglected for high frequencies due to 1/f in equation 2.39. Generally flicker noise in p-channel devices is significantly smaller than in n-channel devices for equal device dimensions.

In design practice p-channel devices are mostly chosen larger than nchannel devices in oder to compensate the difference of the charge carriers mobilities. Hence noise is mostly determined by n-channel devices.

The meaning of the noise level in this work is given by the obtainable resolution qualified by the the signal to noise ratio as it is typical of all analogue systems. If the noise level is smaller than 1 mV  $/\sqrt{Hz}$  the noise of the components would play a minor rule, because in mixed-signal systems the analogue signals are superimposed by noise caused by component switching of comparators and digital cells. This noise contribution is expected to be higher than the component noise. Hence the hysteresis of the comparators must be adjusted in respect of the highest noise source.

Concerning the aspired reduction of current and voltage within the components the input voltage noise becomes worse with smaller  $V_{gs}$  and therefore the SNR gets worse. Furthermore the reduction of the power supply voltage decreases the maximum signal range and worsens also the SNR.

### 2.2 Analogue Comparator

### 2.2.1 Simple Comparator

For basic investigations of comparators a conventional and simple topology with an additional node for biasing was at first chosen. Through this it was possible to drive the circuit in different modes, only by changing the supply current. In more complex circuits this is more difficult or only possible with limitations. By choosing the saturation points of the transistors at minimal levels, it was possible to apply smallest power supply voltages. For this the dimensions of the devices were arranged so that saturation points can be achieved in a range of 100 mV to 150 mV. The comparator was supplied by one positive power supply voltage and one bias current. Of most interest was a circuit that works with a minimum of current. Usual comparators are typically driven with bias currents in the range of 10  $\mu$ A to 1 mA. In this range the transistors are normally operating in the strong inversion region. If the circuit is driven with much less current, then it is possible to operate in the weak or moderate inversion region.

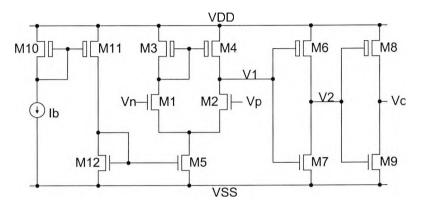

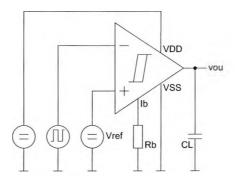

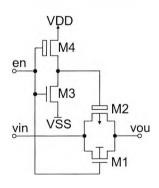

Figure 2.4: Simple comparator

The architecture of a simple comparator including one current source is shown in figure 2.4. The input of the comparator consists of a n-channel differential pair M1 and M2 and a n-channel current source M5. The transistors M6 to M9 build the output buffers by two inverters. M10 to M12 are two current mirrors for the current source. Due to the use of only one input stage, this comparator has no input rail-to-rail functionality. For weak or moderate inversion operation, the input voltage can be equal or smaller than the threshold voltage. In the weak inversion region with very small supply currents the common mode input range can be expressed by

$$V_{dsat} + V_{gs} \le V_{cm} \le V_{DD} \tag{2.40}$$

where  $V_{dsat}$  is the saturation voltage of the current source,  $V_{cm}$  is the common mode voltage and  $V_{gs}$  is the gate-source voltage, which can be smaller than  $V_{th}$  resulting in an enhanced common mode input range.

For strong inversion operation the input common mode range is given by

$$V_{th} + V_{eff} + V_{ds} \le V_{cm} \le V_{DD}.$$

(2.41)

The value of  $V_{ds}$  in equation 2.41 is larger than the saturation voltage of equation 2.40 and  $V_{th} + V_{eff}$  is larger than  $V_{gs}$  of equation 2.40. Therefore the supply voltage must be increased for strong inversion operation.

If the circuit is biased in the weak inversion region, with some 10 nA, then saturation occurs at about  $V_{dsat_{M5}} \approx 6 \cdot V_T \approx 150 mV$ . It is feasible to drive the input transistor below the threshold voltage due the the small bias current. From equation 2.7 the following equation 2.42 can be derived. It gives the dependencies for the minimum effective gate-source voltage  $V_{eff} = V_{gs} - V_{th}$ .

$$V_{eff} = n \cdot V_T \cdot ln\left(\frac{I_D}{I_S}\frac{L}{W}\right)$$

(2.42)

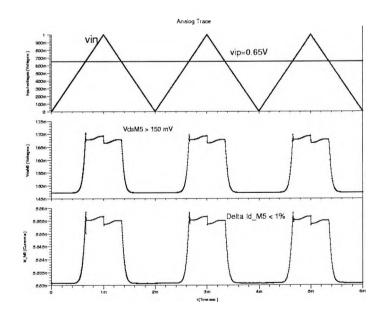

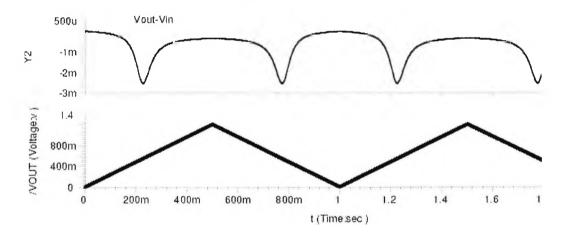

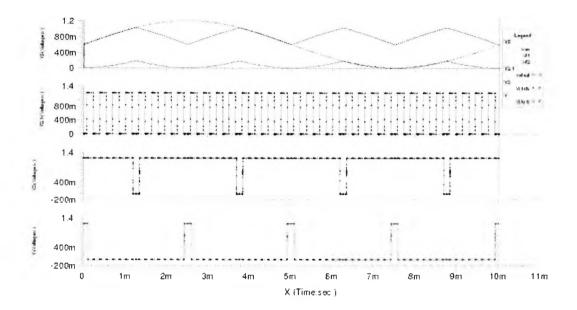

In the time domain simulation (Fig. 2.5) the drain current and the drainsource voltage of the current source M5 are depicted. Referring to a fixed reference voltage vip, the potential at the drain of M5 is adjusted to a minimum voltage of 150 mV. Smaller reference voltages or smaller signal voltages at vin would reduce this potential. In this case the current source would leave the saturation region.

Figure 2.5: Time domain simulation of the simple comparator

The simulation result of figure 2.5 shows also the transition from the saturation region to the triode region. Assuming  $n \approx 1.5$ ,  $V_T = 150 m V @25^{\circ}C$ ,  $\frac{W}{L} = 1$ , a coefficient of the current ratio  $I_D/I_S$  of  $\approx 0.1$  and neglecting the channel length modulation, then  $V_{gs}$  of M1 can be calculated by equation 2.43.

$$V_{gs_{M1}} = n \cdot V_T \cdot ln(\frac{I_D}{I_S}) + V_{th}$$

$$(2.43)$$

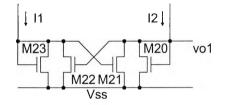

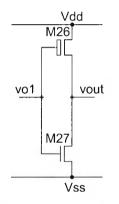

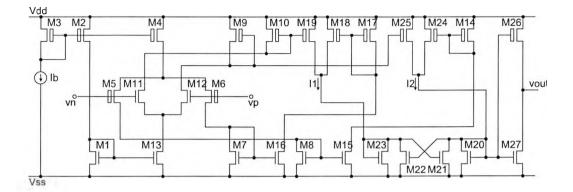

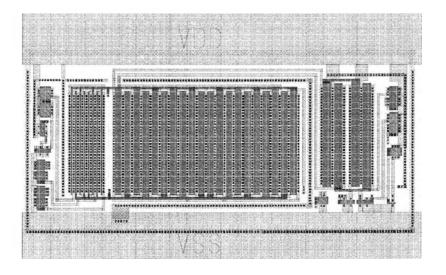

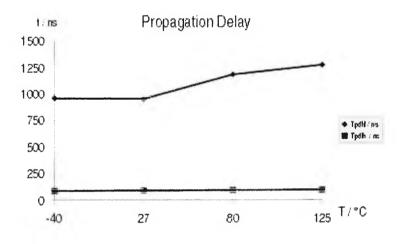

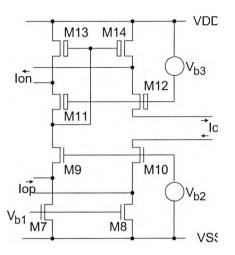

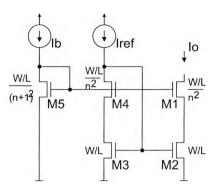

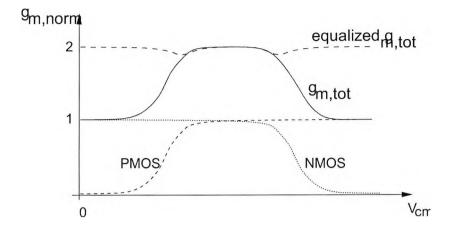

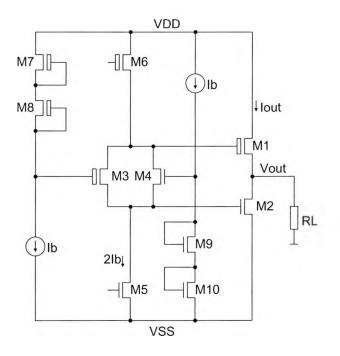

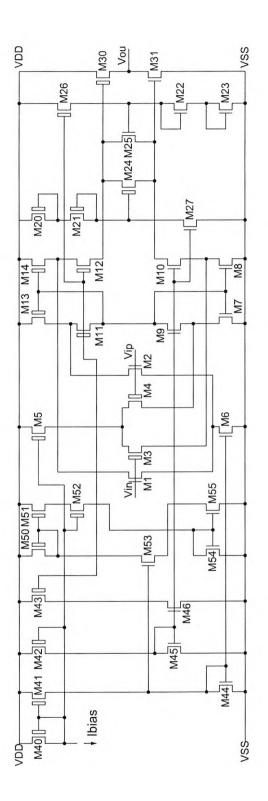

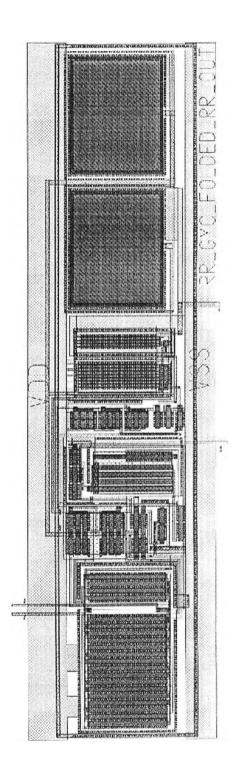

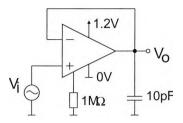

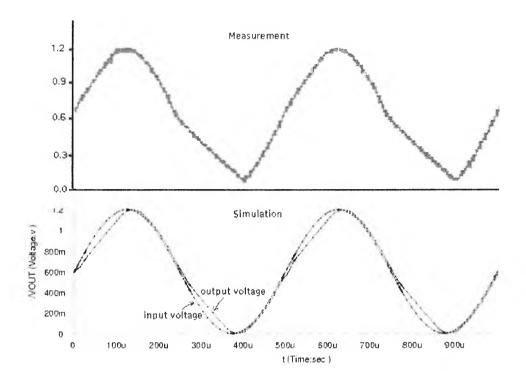

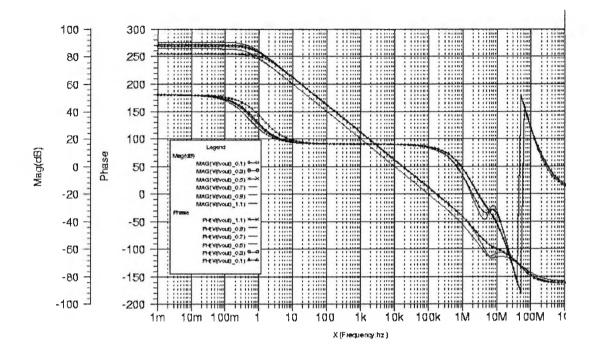

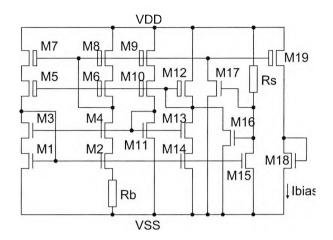

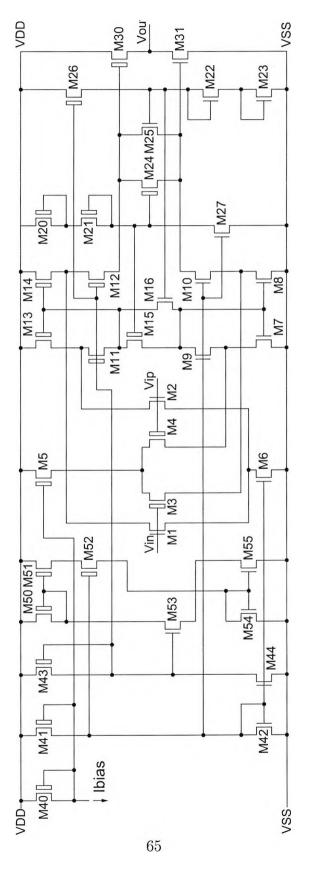

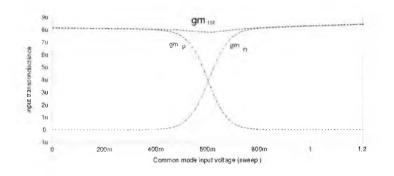

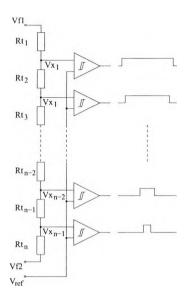

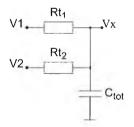

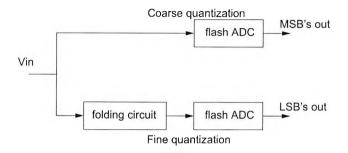

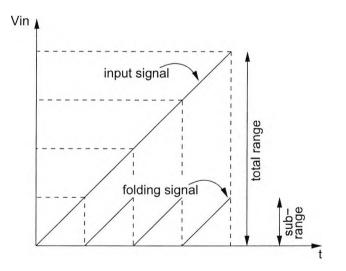

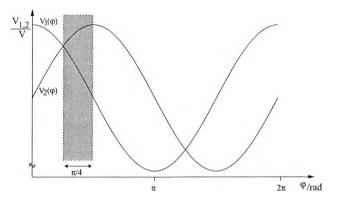

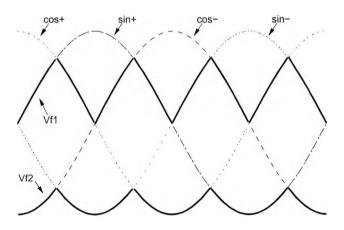

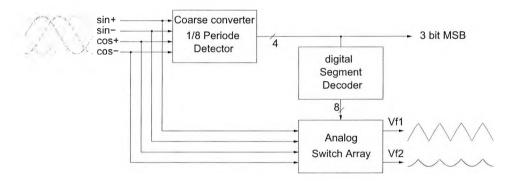

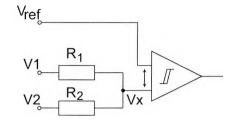

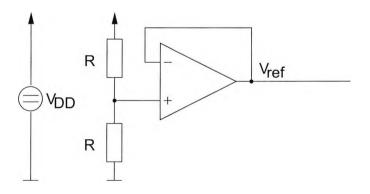

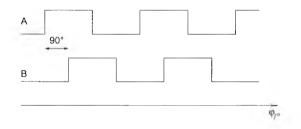

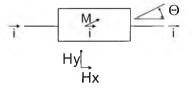

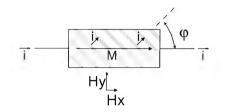

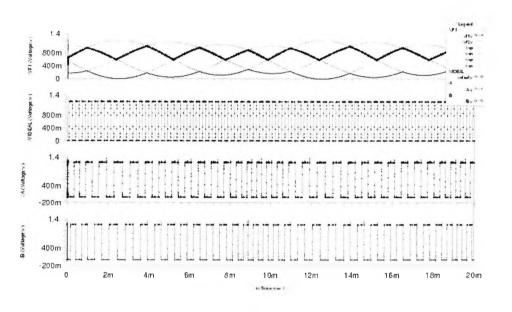

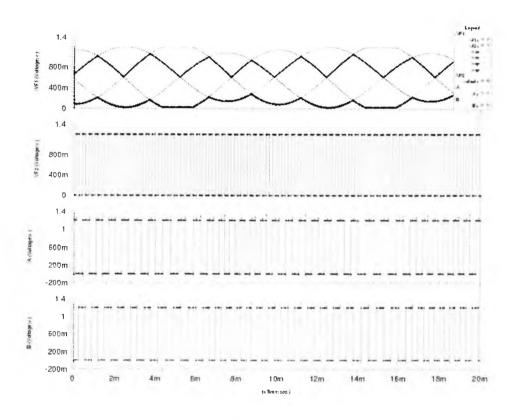

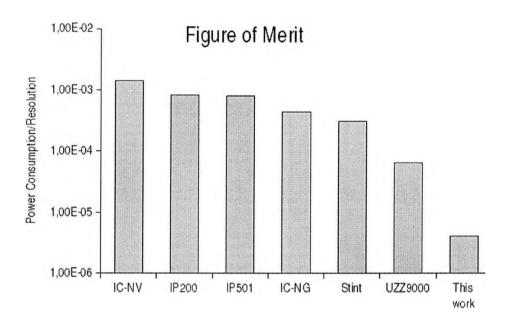

Based on these assumptions the input voltage is given by  $V_{dsat_{M5}} + V_{gs_{M1}} \approx 150mV + 500mV \approx 650mV$ . It can be observed that the circuit can operate with a slightly smaller input voltage, but this influences the current source, which results in slightly smaller currents of the current source. The current source is therefore no longer a stable source.